Implementing Mean Filtering with FPGA: Source Code Provided

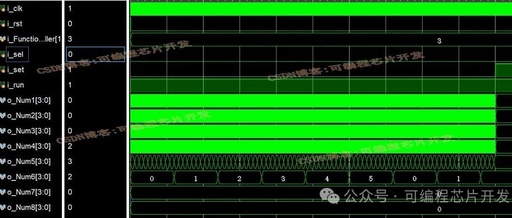

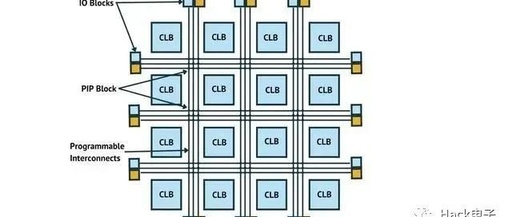

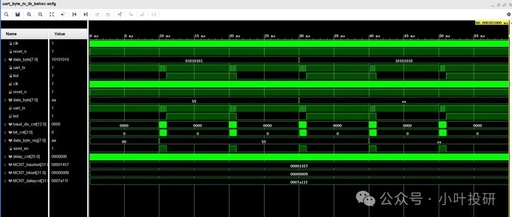

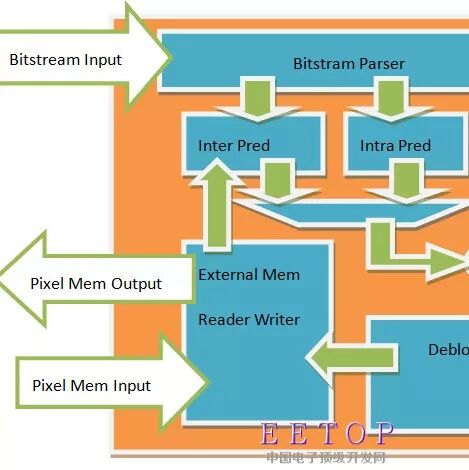

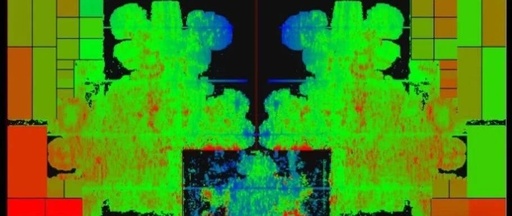

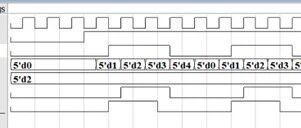

Mean filtering is a fundamental digital signal processing technique commonly used for image and signal denoising. This article will detail how to implement a simple yet efficient mean filter using the Verilog hardware description language. Basic Principles of Mean Filtering The core idea of mean filtering is to replace the value of a pixel with … Read more