Introduction to Excellent Verilog/FPGA Open Source Projects (Thirteen) – I2C

0 Introduction to I2C

Official Website

❝

The I2C bus specification was written by Philips Semiconductors, which later became NXP Semiconductors, and is now the maintainer of the I2C bus specification.

Unfortunately, the latest I²C bus specification, NXP document version 6.0, dated April 4, 2014, is no longer publicly available on the NXP site. It can be found at

❝

https://www.nxp.com/docs/en/user-guide/UM10204.pdf

or can be downloaded after logging in:

❝

https://www.nxp.com/webapp/Download?colCode=UM10204&location=null.

History of the I2C Bus

❝

https://www.esacademy.com/en/library/technical-articles-and-documents/miscellaneous/i2c-bus/general-introduction/history-of-the-i2c-bus.html

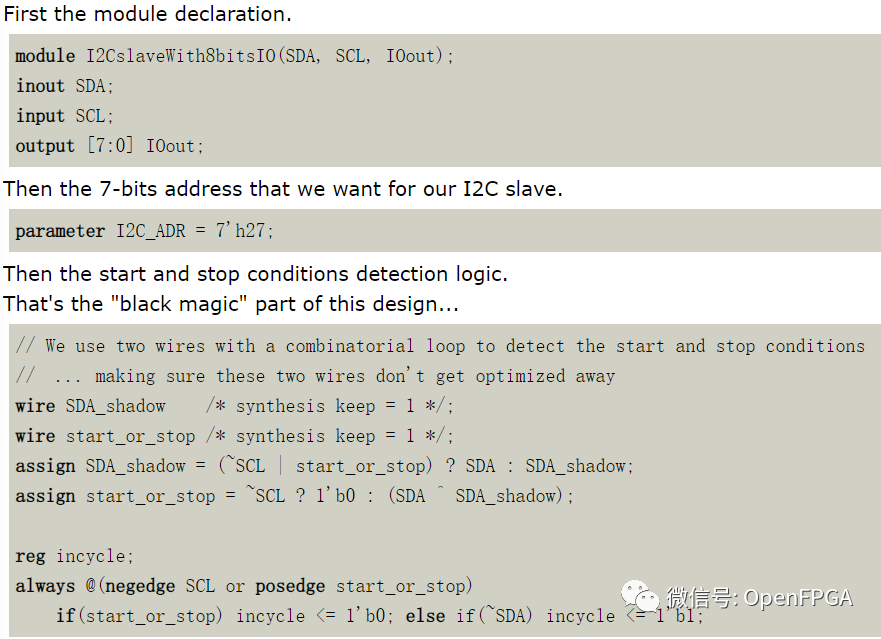

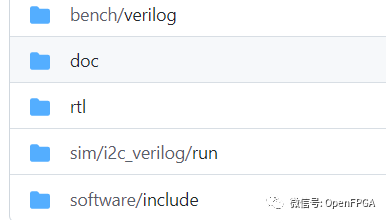

1 I2C on fpga4fun

❝

https://www.fpga4fun.com/I2C_2.html

Detailed design process:

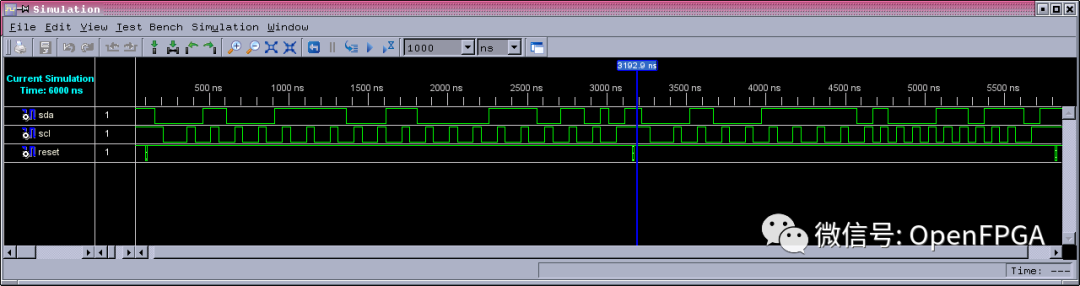

Complete simulation program:

2 alexforencich’s verilog-i2c

❝

https://github.com/alexforencich/verilog-i2c

Alex’s project needs no introduction; his work on networking and PCIe is among the best in terms of completeness.

Let’s take a look at the files included in this project:

axis_fifo.v : AXI stream FIFO

i2c_init.v : Template I2C bus init state machine module

i2c_master.v : I2C master module

i2c_master_axil.v : I2C master module (32-bit AXI lite slave)

i2c_master_wbs_8.v : I2C master module (8-bit Wishbone slave)

i2c_master_wbs_16.v : I2C master module (16-bit Wishbone slave)

i2c_slave.v : I2C slave module

i2c_slave_axil_master.v : I2C slave module (parametrizable AXI lite master)

i2c_slave_wbm.v : I2C slave module (parametrizable Wishbone master)

i2c_init module

Template module for initializing peripherals via I2C. This is used when one or more peripherals (i.e., PLL chips, jitter attenuators, clock multiplexers, etc.) need to be initialized at power-up without using a general-purpose processor.

i2c_master module

I2C master module with AXI interface.

i2c_master_axil module

I2C master module with a 32-bit AXI lite slave interface.

i2c_master_wbs_8 module

I2C master module with an 8-bit Wishbone slave interface.

i2c_master_wbs_16 module

I2C master module with a 16-bit Wishbone slave interface.

i2c_slave module

I2C slave module with AXI interface.

i2c_slave_axil_master module

I2C slave module with a parametrizable AXI lite master interface.

i2c_slave_wbm module

I2C slave module with a parametrizable Wishbone master interface.

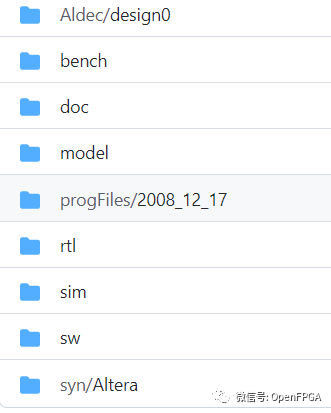

3 opencores i2c

❝

https://opencores.org/projects/i2c

❝

https://opencores.org/projects/i2c_master_slave_core

❝

https://opencores.org/projects/i2cslave

❝

https://github.com/trondd/oc-i2c

Features

-

Both Master and slave operation

-

Both Interrupt and non-interrupt data transfers

-

Start/Stop/Repeated Start generation

-

Fully supports arbitration process

-

Software programmable acknowledge bit

-

Software programmable timeout feature

-

Programmable address register

-

Programmable SCL frequency

-

Soft reset of I2C Master/Slave

-

Programmable maximum SCL low period

-

Synthesis core

Synthesis Results

Synthesis results for various targets.

A54SX16ATQ100-std: 352 Modules @ 58MHz

FLEX: EPF10K50ETC144-3: 294 LCELLs @ 82MHz

ACEX: EPF20K30ETC144-3: 257 ATOMs @ 74MHz

Spartan-II: 2S15CS144-5: 229 LUTs @ 82MHz

Virtex-E: XCV50ECS144-8: 230 LUTs @ 118MHz

4 freecores i2c

❝

https://github.com/freecores/i2c

❝

https://github.com/freecores/i2cslave

Although there is no detailed documentation, the entire project is still quite complete, and the logic of I2C is not complex, making it manageable even without documentation.

5 hhping i2c_code

❝

https://github.com/hhping/i2c_code

This set of I2C code has been verified on the board. It has been validated on the Kyushu detector version.

6 BNUGYX Verilog_i2c_eeprom

❝

https://github.com/BNUGYX/Verilog_i2c_eeprom

❝

https://github.com/mcgodfrey/i2c-eeprom

I2C communication implementation for EEPROM read/write.

First, write a fixed character, then read this character and display it on a digital tube.

7 splinedrive i2c_sdd1306_framebuffer

❝

https://github.com/splinedrive/i2c_sdd1306_framebuffer

This is an FPGA-based I2C SSD1306 OLED design! It includes an I2C master controller, frame buffer, font rendering unit, RX unit…

Just send data at 115200 baud through the serial port to the FPGA, and these characters will be displayed on the OLED!

8 tmatsuya i2c_edid

❝

https://github.com/tmatsuya/i2c_edid

I2C ROM for EDID (Extended Display Identification Data) IP CORE

Description

-

This project aims to transmit display modes to video source target devices using the I2C DDC protocol.

-

Suitable for HDMI camera capture device or video switcher developers.

Features

-

Supports I2C slave protocol and EDID (Extended Display Identification Data) ROM.

-

8-bit addressing (maximum 256 bytes).

Directory Structure

/boards/ Top-level design files, constraint files, and Makefiles

/cores/ Core library

/software/ Software and data files

Conclusion

There are many open-source projects related to I2C, and it should be easy for many experts to independently write an I2C bus. The first two projects are the most commonly used and need no further introduction. The later projects target specific scenarios for EDID and EEPROM. After the introduction of these projects, I believe everyone should feel more confident about implementing I2C on FPGA.

Finally, thanks to all the experts for their open-source projects, which have greatly benefited us. If you have any projects of interest, feel free to leave a message in the background or add me on WeChat to leave a message. That’s all for today; I am the overworked Sui Sui Si, and I look forward to seeing you in the next article.

Merry Christmas

Introduction to Excellent Verilog/FPGA Open Source Projects (Ten) – H.264 and H.265

Introduction to Excellent Verilog/FPGA Open Source Projects (Nine) – DP (Revised Version)

Introduction to Some Excellent Websites for Beginners in FPGA (New Additions)

Introduction to Excellent Verilog/FPGA Open Source Projects (Eight) – HDMI

Introduction to Excellent Verilog/FPGA Open Source Projects (Seven) – CAN Communication

Introduction to Excellent Verilog/FPGA Open Source Projects (Six) – MIPI

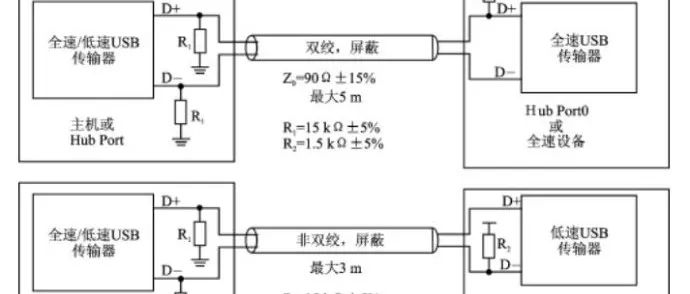

Introduction to Excellent Verilog/FPGA Open Source Projects (Five) – USB Communication

Introduction to Excellent Verilog/FPGA Open Source Projects (Four) – Ethernet

Introduction to Excellent Verilog/FPGA Open Source Projects (Three) – Projects from Major Companies

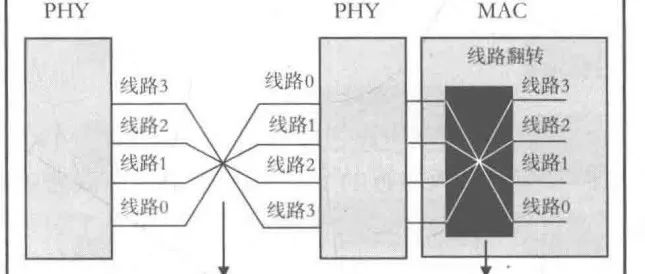

Serial Bus Technology (Two) – Advanced Design Concepts in Serial Buses and Introduction to SerDes/PMA

Serial Bus Technology (One) – Structure of Serial Buses (Taking PCIe as an Example)

Introduction to Excellent Verilog/FPGA Open Source Projects (Twelve) – Making FPGA Fun

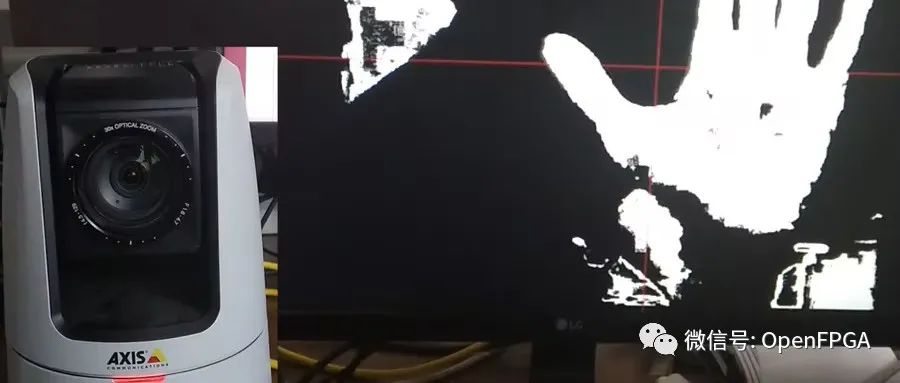

Real-time Object Tracking Using a PTZ Camera (Skin Color Tracking)