Basics of Assembly: Hands-On with General-Purpose Registers

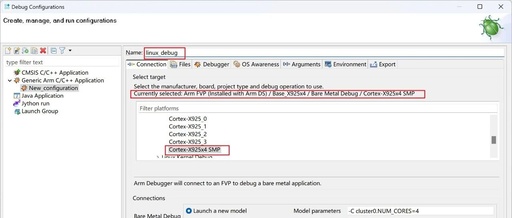

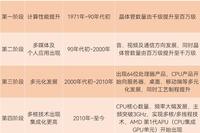

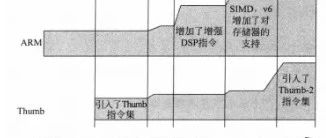

In the previous article, it was mentioned that in assembly, the content of registers is modified through assembly instructions to control the CPU’s operation. Several classifications of registers were also discussed.Understanding the concepts can be a bit dry, so today we will look at several registers through debugging on a PC, and also modify the … Read more