🔍See the end of the article for program acquisition methods

📶The project includes complete programs, documentation, references, and operation videos

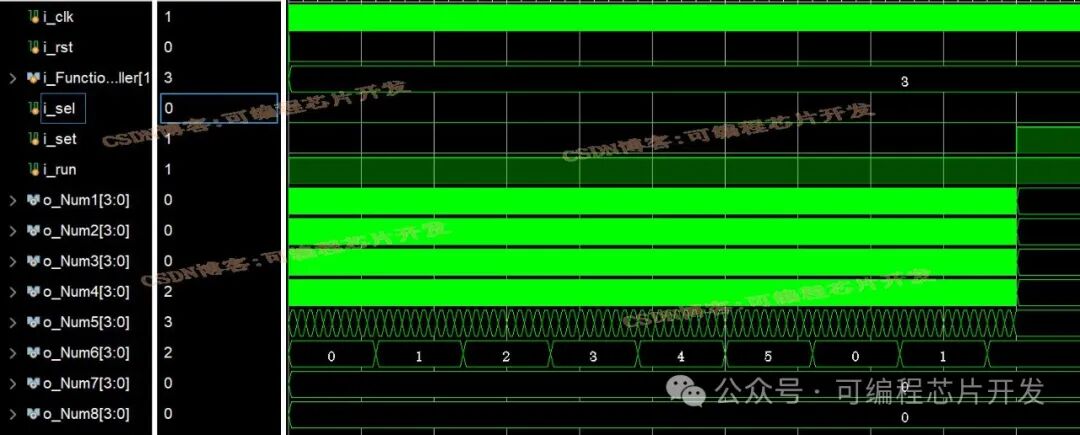

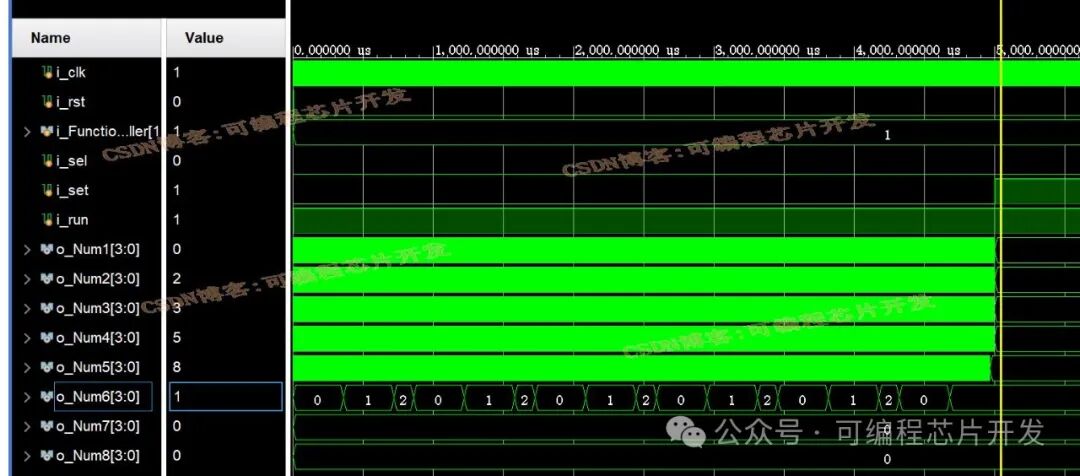

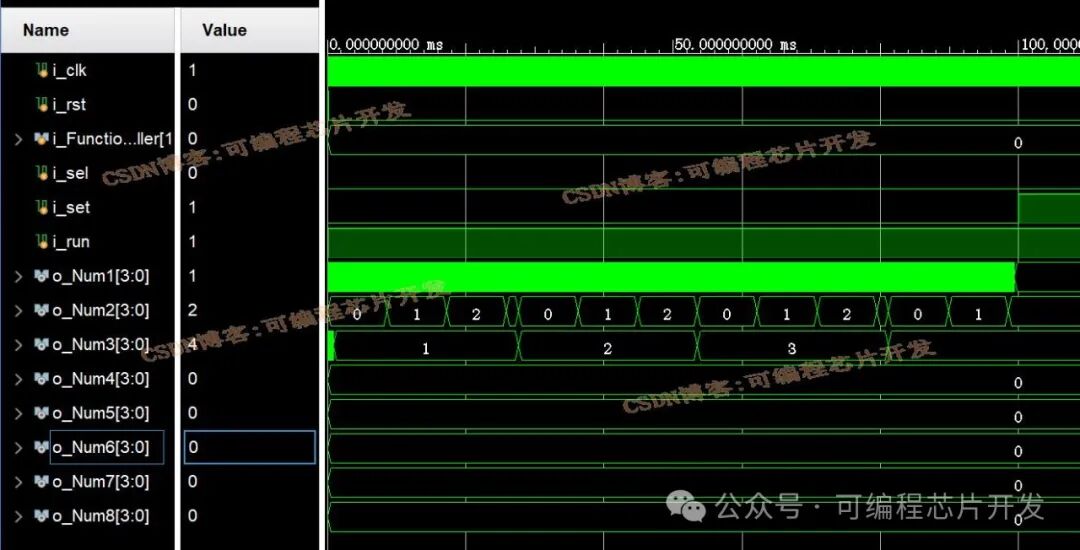

🌠Simulation Conclusion Preview

The testing results using Vivado 2022.2 are as follows:

⚡Program Function Description

<span><span>The functions and principles of this program are as follows:</span></span>

1. Basic functions of the system

Clock display: hours, minutes (24-hour format)

Calendar display: year, month, day

Stopwatch function: accurate to 0.01 seconds, supports start/pause/reset

2. Mode switching function

Our control input has 5 pins, with the analysis of functions as follows:

i_Function_Controller=0; Display year, month, day

i_sel: Select the digit to be adjusted.

i_set: Counter, adjust the digit at the selected position.

During adjustment, first select i_sel, press the button once, the position to be adjusted will move once, then move to the desired position, release i_sel, and then press i_set to adjust the displayed number.

i_run: Not used

i_Function_Controller=1; Display time, hours, minutes, seconds

i_sel:

i_set:

i_run:

During normal operation, the above three settings input 0, 0, 1 respectively

When time adjustment is needed, set i_run=0, then set i_sel to select the corresponding digit to be adjusted, and set i_set to set the specific value, where if i_set is set for seconds, seconds will be cleared directly.

Note that because the time part counts to 24 hours, the year, month, and day are only incremented then, so for year, month, and day, i_run is not used; it is driven by the date module.

i_Function_Controller=3; Control of the stopwatch

i_sel: Clear

i_set: Pause

i_run: Start stopwatch timing

✨Partial Program

<span><span>Some core program content is as follows:</span></span>

`timescale 1ns / 1ps`timescale 1ns / 1ps//// Company: // Engineer: // // Create Date: 14:45:46 04/09/2014 // Design Name: // Module Name: tops // Project Name: // Target Devices: // Tool versions: // Description: //// Dependencies: //// Revision: // Revision 0.01 - File Created// Additional Comments: ////module tops( i_clk, i_rst, i_Function_Controller, i_sel, i_set, i_run, o_Num1, o_Num2, o_Num3, o_Num4, o_Num5, o_Num6, o_Num7, o_Num8 );input i_clk;input i_rst;input[1:0] i_Function_Controller;input i_sel;input i_set;input i_run;output[3:0]o_Num1;output[3:0]o_Num2;output[3:0]o_Num3;output[3:0]o_Num4; output[3:0]o_Num5;output[3:0]o_Num6;output[3:0]o_Num7;output[3:0]o_Num8; wire Clock_mb;wire Clock;clock_div clock_div_u( .i_clk (i_clk), .i_rst (i_rst), .i_sel (1'b0), .o_clock1 (Clock_mb), .o_clock2 (Clock) );//======================================================================wire CLK_Year;wire[3:0]ym_Num1;wire[3:0]ym_Num2;wire[3:0]ym_Num3;wire[3:0]ym_Num4; wire[3:0]ym_Num5;wire[3:0]ym_Num6;wire[3:0]ym_Num7;wire[3:0]ym_Num8;year_month year_month_u( .i_clk (CLK_Year), .i_rst (i_rst), .i_sel (i_sel), .i_set (i_set), .o_Num1 (ym_Num1), .o_Num2 (ym_Num2), .o_Num3 (ym_Num3), .o_Num4 (ym_Num4), .o_Num5 (ym_Num5), .o_Num6 (ym_Num6), .o_Num7 (ym_Num7), .o_Num8 (ym_Num8) );//======================================================================wire[3:0]tm_Num1;wire[3:0]tm_Num2;wire[3:0]tm_Num3;wire[3:0]tm_Num4; wire[3:0]tm_Num5;wire[3:0]tm_Num6;wire[3:0]tm_Num7;wire[3:0]tm_Num8;times times_u( .i_clk (Clock), .i_rst (i_rst), .i_run (i_run), .i_sel (i_sel), .i_set (i_set), .o_Num1 (tm_Num1), .o_Num2 (tm_Num2), .o_Num3 (tm_Num3), .o_Num4 (tm_Num4), .o_Num5 (tm_Num5), .o_Num6 (tm_Num6), .o_CLK_Year (CLK_Year), .CNT () );assign tm_Num7 = 4'd0;assign tm_Num8 = 4'd0;//======================================================================wire[3:0]mb_Num1;wire[3:0]mb_Num2;wire[3:0]mb_Num3;wire[3:0]mb_Num4; wire[3:0]mb_Num5;wire[3:0]mb_Num6;wire[3:0]mb_Num7;wire[3:0]mb_Num8;miaobiao miaobiao_u( .i_clk (Clock_mb), .i_rst (i_rst), .i_run (i_run), .i_pause (i_set), .i_clear (i_sel), .o_Num1 (mb_Num1), .o_Num2 (mb_Num2), .o_Num3 (mb_Num3), .o_Num4 (mb_Num4), .o_Num5 (mb_Num5), .o_Num6 (mb_Num6) );assign mb_Num7 = 4'd0;assign mb_Num8 = 4'd0;//=====================================================================reg[3:0]o_Num1;reg[3:0]o_Num2;reg[3:0]o_Num3;reg[3:0]o_Num4; reg[3:0]o_Num5;reg[3:0]o_Num6;reg[3:0]o_Num7;reg[3:0]o_Num8; always @(posedge i_clk or posedge i_rst)begin if(i_rst) begin o_Num1 <= 4'd0; o_Num2 <= 4'd0; o_Num3 <= 4'd0; o_Num4 <= 4'd0; o_Num5 <= 4'd0; o_Num6 <= 4'd0; o_Num7 <= 4'd0; o_Num8 <= 4'd0; endelse begin if(i_Function_Controller == 2'b00) begin o_Num1 <= ym_Num1; o_Num2 <= ym_Num2; o_Num3 <= ym_Num3; o_Num4 <= ym_Num4; o_Num5 <= ym_Num5; o_Num6 <= ym_Num6; o_Num7 <= ym_Num7; o_Num8 <= ym_Num8; end if(i_Function_Controller == 2'b01) begin o_Num1 <= tm_Num1; o_Num2 <= tm_Num2; o_Num3 <= tm_Num3; o_Num4 <= tm_Num4; o_Num5 <= tm_Num5; o_Num6 <= tm_Num6; o_Num7 <= tm_Num7; o_Num8 <= tm_Num8; end if(i_Function_Controller == 2'b11) begin o_Num1 <= mb_Num1; o_Num2 <= mb_Num2; o_Num3 <= mb_Num3; o_Num4 <= mb_Num4; o_Num5 <= mb_Num5; o_Num6 <= mb_Num6; o_Num7 <= mb_Num7; o_Num8 <= mb_Num8; end endend

endmodule00X6_004m🌍Program Acquisition Method

Click the bottom left corner of WeChat to read the original text