Source: EETOP BBS Author: eebinqiu

Original: http://bbs.eetop.cn/thread-628991-1-1.html

This was first written in 2011, initially supporting only 640×480 resolution on the Cyclone4 E40, without implementing a deblocking filter, and the frame rate was only 25fps.

Recently, I took on a project for an H.264 FPGA decoder for drones, which required implementing 720p at 60fps with a deblocking filter. After several months of modifications, it is finally complete.

Here, I am sharing the original source code and project for the Cyclone4 E40, as well as an SD card image that can decode 720p at 60fps on the Mill Zturn Zynq7020 development board and the Black Gold Zynq 7020. Friends with the board can give it a try.

The entire system on the Zynq7020 occupies 70%, with the IP occupying 57%. It uses a significant amount of resources, but the parallelism is high, allowing for 1080p decoding at 75M.

Below is the latest version of the datasheet

Function Overview:

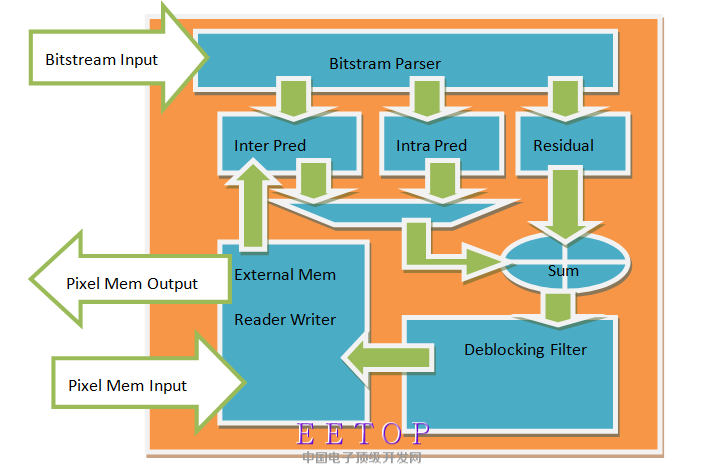

The Osenlogic OSD10 receives the H.264 NAL stream from a FIFO from external memory, decodes it to YUV 4:2:0, and then stores it to external memory.

The OsenLogic OSD10 includes a bitstream parser (exp-golomb and CAVLC), IDCT/Iquant (residual), intra-predictor and inter-predictor, and a deblocking filter.

All are implemented in Verilog HDL. The decoder can operate without a CPU or with a CPU.

Interface Signals

|

Signal Name |

Direction |

Description |

|

rst_n |

Input |

Global reset |

|

clk |

Input |

Main decoder clock |

|

ext_mem_rd_clk |

Input |

The clock associated with the external memory reader |

|

ext_mem_wr_clk |

Input |

The clock associated with the external memory writer |

|

ena |

Input |

Enable the decoder |

|

stream_mem_data_in |

Input |

The stream data from stream FIFO |

|

stream_data_valid |

Input |

High when stream data is available from stream FIFO |

|

stream_mem_rd |

Output |

High when the decoder requests data from stream FIFO |

|

ext_mem_init_done |

Input |

High when external memory has finished initialization |

|

ext_mem_writer_burst |

Output |

Indicates the start of write burst |

|

ext_mem_burst_len_minus1 |

Output |

When ext_mem_writer_burst_len_minus1 is High, indicates the length of write burst |

|

ext_mem_writer_ready |

Input |

High when external memory is able to accept data from memory |

|

ext_mem_writer_addr |

Output |

Valid when ext_mem_writer_burst is high, indicates the address writing to external memory |

|

ext_mem_writer_data |

Output |

The data from the decoder to external memory |

|

ext_mem_writer_valid |

Output |

High when the data from the decoder is available to external memory |

|

ext_mem_reader_burst_ready |

Input |

High when external memory is ready to accept data from the decoder |

|

ext_mem_reader_burst |

Output |

Indicates the start of read burst |

|

ext_mem_reader_burst_len_minus1 |

Output |

When ext_mem_reader_burst_len_minus1 is High, indicates the length of read burst |

|

ext_mem_reader_ready |

Output |

High when the decoder is able to accept data from external memory |

|

ext_mem_reader_data |

Input |

Data being read from external memory |

|

ext_mem_reader_valid |

Input |

High when external memory data is available |

|

pic_width_in_mbs |

Output |

Total MBs in width |

|

pic_height_in_map_units |

Output |

Total MBs in height |

|

total_mbs_one_frame |

Output |

Total MBs in frame |

|

start_of_frame |

Output |

High when start of decoding frame |

|

end_of_frame |

Output |

High when end of a decoding frame |

|

pic_num |

Output |

Total decoded frames |

|

mb_index |

Output |

Current decoding mb_index |

Specifications

|

Model |

Osen Logic OSD10 H.264 decoder |

|

Profile |

Baseline |

|

Level |

3.1 |

|

Input Format |

H.264 NAL stream |

|

Output Format |

YUV 4:2:0 |

|

Slice type supported |

I, SI, P, SP |

|

Entropy Coding |

CAVLC |

|

Supported frame sizes |

Max: 1920×1088 Min: 640×480 |

|

Supported bitrate |

0 to 10Mbps No decode rate control |

|

Max supported resolution at max frame rate |

1920×1088 @ 30fps, decoder clock working at 75M |

|

Required external memory size |

32Mbyte |

|

External memory reader interface data width |

64bit |

|

External memory writer interface data width |

32bit |

Osenlogic_OSD10_datasheet.pdf

(Please log in to the forum to download the datasheet)

Source Code and SD Card Image

Myir Zynq 7020 or Black Gold AX7020 can play the 1080p image. You can use dd or Win32DiskImager to write to the SD card, SD >= 2GB

(Source code and image files can be downloaded from the forum, http://bbs.eetop.cn/thread-628991-1-1.html)

Click to read the original text and log in to the forum to download the source code

Click to read the original text and log in to the forum to download the source code