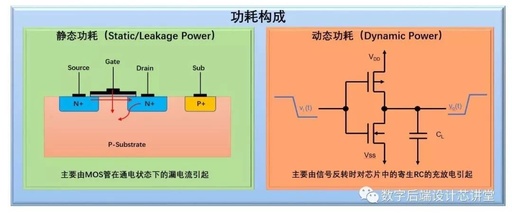

Low Power Design Methods – Power Gating Design (Part 3)

State Retention and Restoration Methods Continuing from the previous text Low Power Design Methods – Power Gating Design (Part 1) Low Power Design Methods – Power Gating Design (Part 2) Given the power switch structure and isolation strategy, power gating can be applied to logic blocks. However, unless a retention strategy is employed, all state … Read more