Chapter 6 Low Power Design Analysis (Part 1) – The Theory and Practice of IR Drop and EM

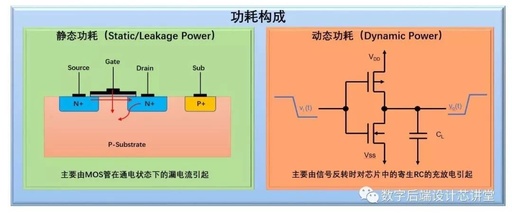

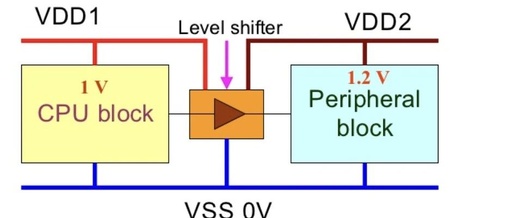

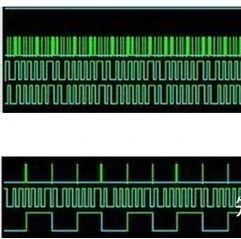

With the increase in device density and clock frequency of chips under advanced processes, power consumption has also significantly increased. At the same time, the supply voltage and transistor threshold voltage have been reduced, leading to significant leakage current. High power consumption can cause excessive temperature during device operation, reducing reliability due to electromigration and … Read more