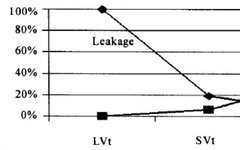

Introduction to Low Power Design in Digital ICs (Part 1): Objectives of Low Power Design and Types of Power Consumption

Follow and star our public account for exciting content Source: Content from http://www.cnblogs.com/IClearner/, Author: IC_learner, thank you. Today, let’s talk about low power design. This low power design is basically at the introductory level, which means it is mostly explained from a theoretical perspective. You could say it is based on what is written in … Read more