Learning JTAG Standard (IEEE1149.1) – Part 2

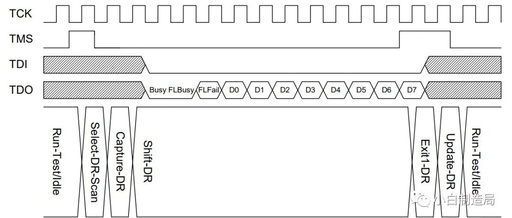

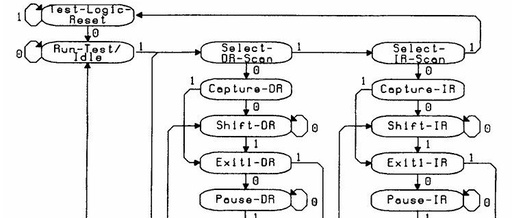

TAP controller The TAP controller is a finite state machine that transitions states based on the TMS signal at the rising edge of TCK, generating control signals to operate the JTAG circuit. The state transition diagram of the TAP controller is shown below: Each state is described as follows: Test-Logic-Reset: The test logic is disabled, … Read more