JTAG Interface Design (5) – JTAG-2

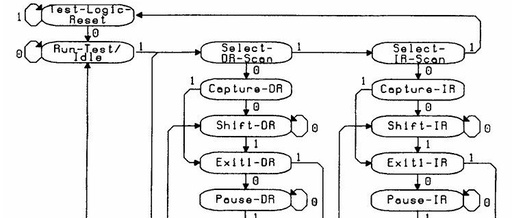

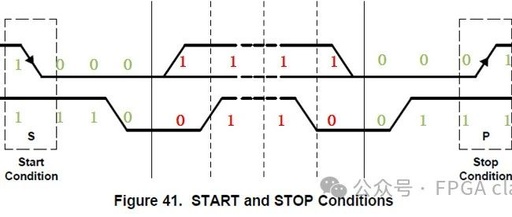

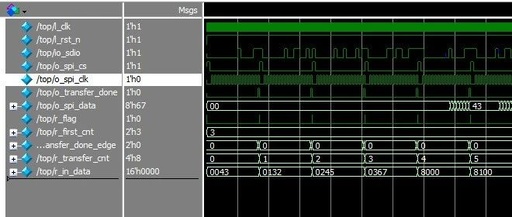

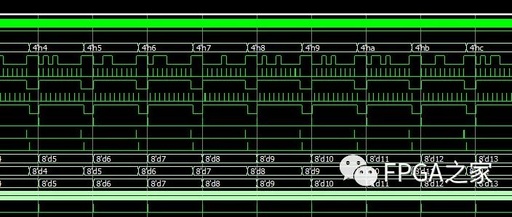

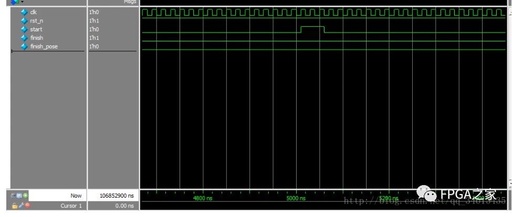

Previously, we discussed the hardware form and basic principles of JTAG. This article uses a JTAG VIP simulation to interpret the waveforms. Referencing SOC Design (4) – Using S Company’s VIP, we first generate an example for JTAG testing: dw_vip_setup -path /home/designware/run_jtag -example jtag_svt/tb_jtag_svt_uvm_basic_sys Enter the simulation directory with cd run_jtag/examples/sverilog/jtag_svt/tb_jtag_svt_uvm_basic_sys, and type in: gmake … Read more