Analysis of JTAG Principles and Its Application in ATE DFT Testing

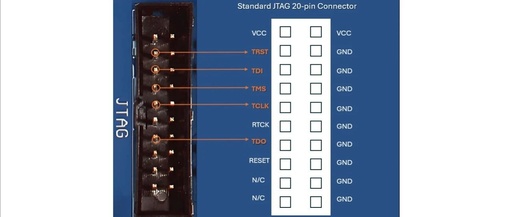

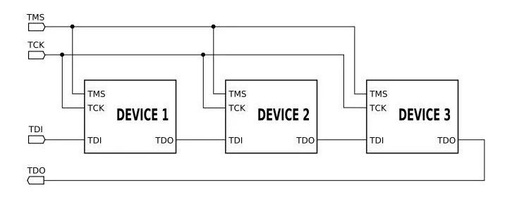

JTAG (Joint Test Action Group) is an international standard testing protocol (IEEE 1149.1) primarily used for testing, debugging, and programming chips, PCBs, and systems. Through a dedicated hardware interface and protocol, it provides non-intrusive access to the internal circuits of chips. The JTAG protocol is widely used in embedded development, hardware verification, and fault diagnosis. … Read more