Exploring FPGA and eFPGA Technologies

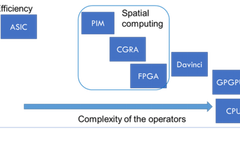

FPGA has become a strategic technology, regarded as the “poor man’s ASIC”, capable of providing customized ICs for a limited number of applications. At the same time, it has gained strategic importance in the following two large and high-growth applications: Cloud Data Centers: Networking, storage, and security; Communication Systems: Base stations and 5G, etc. In … Read more