1. What is a BSDL File?

-

The maximum TCK frequency supported by the current chip

-

Definitions of pin names and numbers

-

Definitions of power, clock, configuration, I/O pins, etc. The type of each pin, such as VCC, GND, CLK, along with the pin names and numbers

-

All available command registers

-

All available data registers, including possible preset values, for example: device IDCODE

2. Obtaining BSDL Files

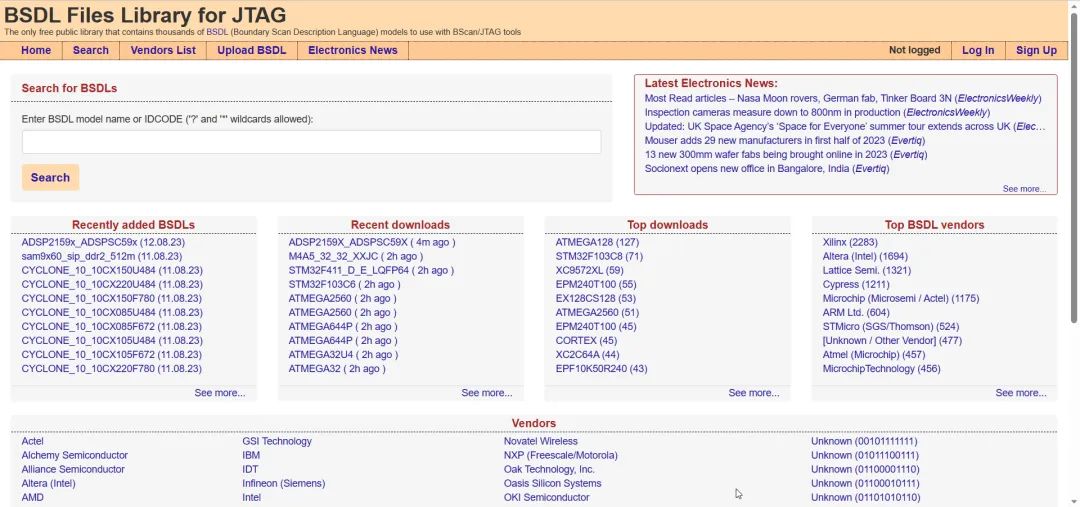

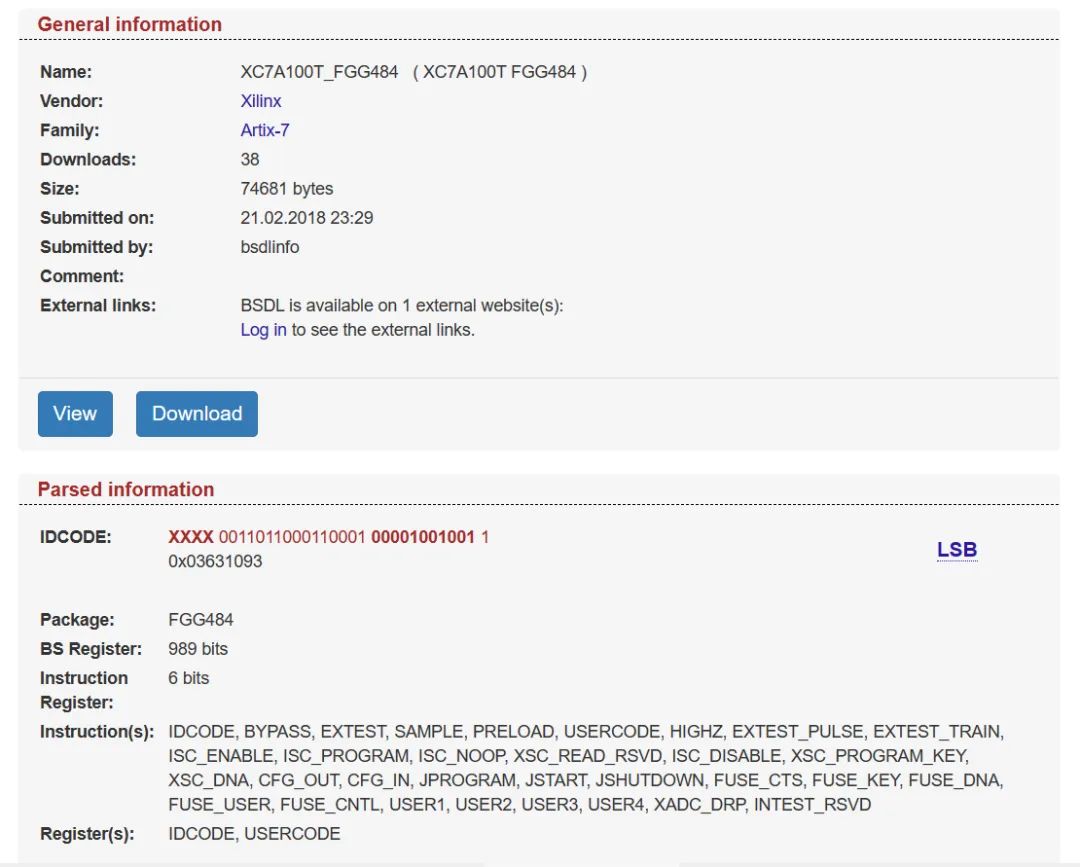

Method 1: BSDL Library

https://www.bsdl.info/

Method 2: Official Websites of Chip Manufacturers

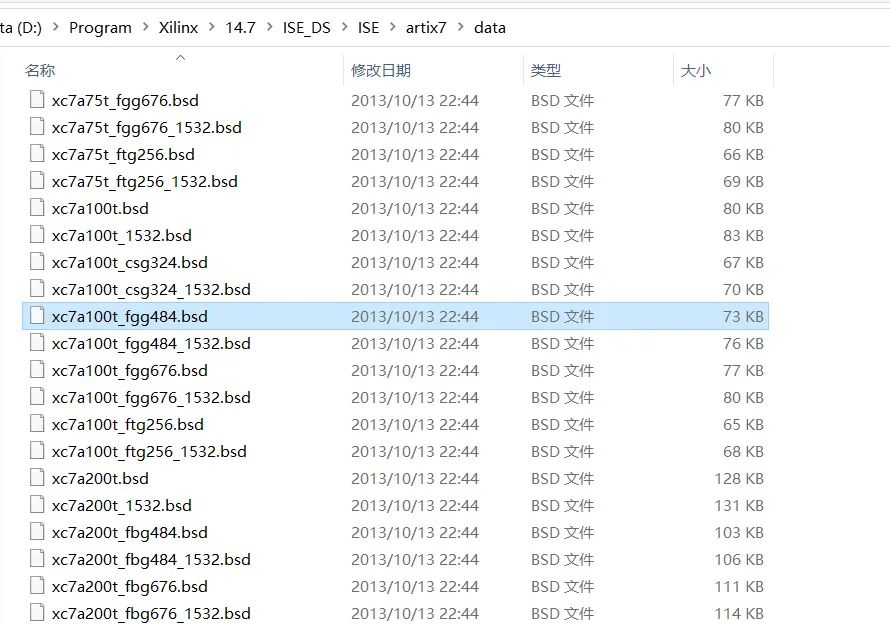

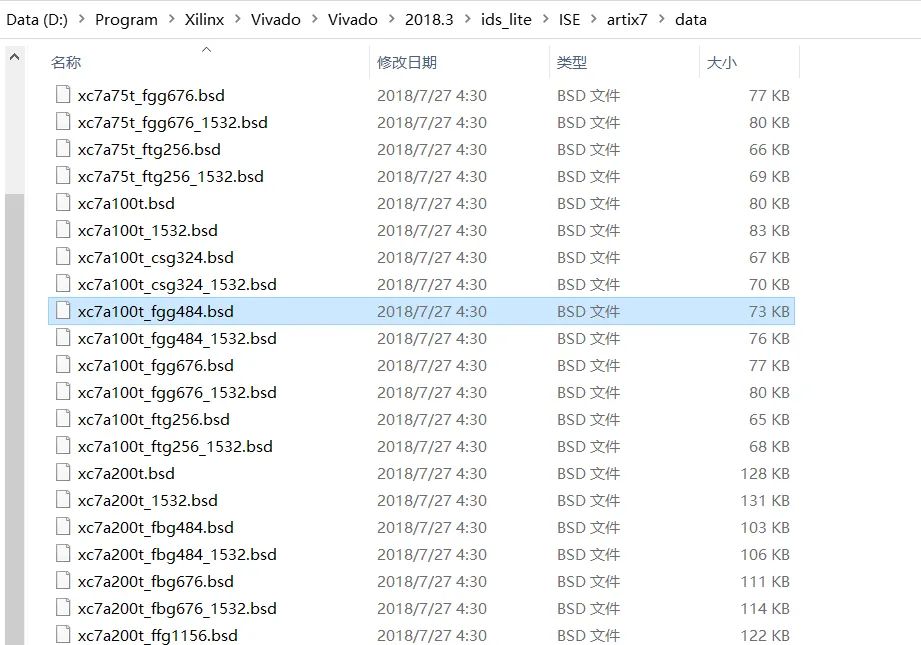

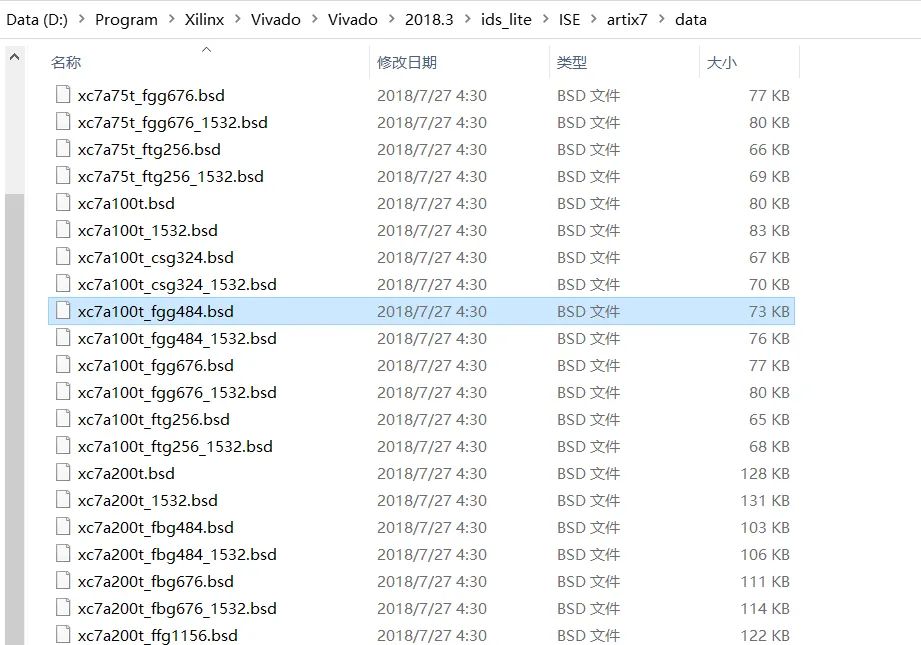

Obtaining Xilinx FPGA BSDL Files

Xilinx\14.7\ISE_DS\ISE\artix7\data

Vivado\Vivado\2018.3\ids_lite\ISE\artix7\data

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/bsdl-models/artix-series-fpgas.html

Obtaining Altera FPGA BSDL Files

https://www.intel.cn/content/www/cn/zh/support/programmable/support-resources/board-layout/bsd-11491.html

https://www.intel.cn/content/www/cn/zh/support/programmable/support-resources/board-layout/bsd-11496.html

Obtaining Microsemi FPGA BSDL Files

https://www.microsemi.com/product-directory/design-resources/1717-bsdl-models

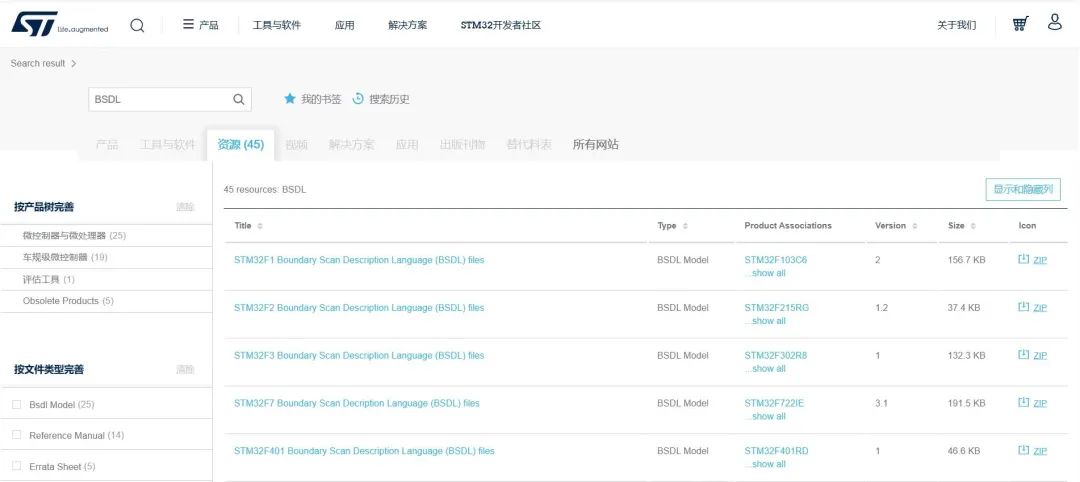

Obtaining ST MCU BSDL Files

STM32F1:

https://www.st.com/content/ccc/resource/technical/ecad_models_and_symbols/bsdl_model/75/4a/50/d0/ad/aa/49/92/stm32f1_bsdl.zip/files/stm32f1_bsdl.zip/jcr:content/translations/en.stm32f1_bsdl.zip

STM32F2:

https://www.st.com/content/ccc/resource/technical/ecad_models_and_symbols/bsdl_model/e9/d6/86/75/13/99/46/c8/stm32f2_bsdl.zip/files/stm32f2_bsdl.zip/jcr:content/translations/en.stm32f2_bsdl.zip

STM32F17:

https://www.st.com/content/ccc/resource/technical/ecad_models_and_symbols/bsdl_model/ad/a6/69/0f/70/95/49/92/stm32f7_bsdl.zip/files/stm32f7_bsdl.zip/jcr:content/translations/en.stm32f7_bsdl.zip

3. BSDL File Example

--

-- BSDL File created/edited by BCAD BSD Editor Version 3.1

--

--BSDE:Revision: $Header: /devl/xcs/repo/env/Jobs/iMPACT/data/xc9500/xc95144.bsd,v 1.2 2000/10/24 00:58:57 sanjays Exp $

--BSDE:Description: Xilinx 144 macrocell FastFLASH ISP CPLD

entity XC95144 is

generic (PHYSICAL_PIN_MAP : string := "DIE_BOND" );

port (

PB00_00: inout bit;

PB00_01: inout bit;

PB00_02: inout bit;

........

VSSINT_4: linkage bit;

VSSIO_1: linkage bit;

VSSIO_2: linkage bit;

VSSIO_3: linkage bit;

VSSIO_4: linkage bit;

VSSIO_5: linkage bit;

VSSIO_6: linkage bit;

VSSIO_7: linkage bit;

VSSIO_8: linkage bit;

VSSIO_9: linkage bit

);

use STD_1149_1_1990.all;

attribute PIN_MAP of XC95144 : entity is PHYSICAL_PIN_MAP;

constant DIE_BOND: PIN_MAP_STRING:=

"PB00_00:PAD25," &

"PB00_01:PAD18," &

"PB00_02:PAD19," &

"PB00_03:PAD27," &

"PB00_04:PAD21," &

"PB00_05:PAD22," &

"PB00_06:PAD32," &

"PB00_07:PAD23," &

"PB00_08:PAD24," &

"PB00_09:PAD34," &

........

"VSSIO_3:PAD51," &

"VSSIO_4:PAD80," &

"VSSIO_5:PAD99," &

"VSSIO_6:PAD110," &

"VSSIO_7:PAD120," &

"VSSIO_8:PAD137," &

"VSSIO_9:PAD160";

attribute TAP_SCAN_IN of TDI : signal is true;

attribute TAP_SCAN_OUT of TDO : signal is true;

attribute TAP_SCAN_MODE of TMS : signal is true;

attribute TAP_SCAN_CLOCK of TCK : signal is (1.00e+07, BOTH);

attribute INSTRUCTION_LENGTH of XC95144 : entity is 8;

attribute INSTRUCTION_OPCODE of XC95144 : entity is

"BYPASS ( 11111111)," &

"CONLD ( 11110000)," &

"EXTEST ( 00000000)," &

"FERASE ( 11101100)," &

"FBULK ( 11101101)," &

"FPGM ( 11101010)," &

"FPGMI ( 11101011)," &

"FVFY ( 11101110)," &

"FVFYI ( 11101111)," &

"HIGHZ ( 11111100)," &

"IDCODE ( 11111110)," &

"INTEST ( 00000010)," &

"ISCEN ( 11101000)," &

"SAMPLE ( 00000001)," &

"USERCODE ( 11111101)" ;

attribute INSTRUCTION_CAPTURE of XC95144 : entity is "000XXX01";

attribute INSTRUCTION_DISABLE of XC95144 : entity is "HIGHZ";

attribute IDCODE_REGISTER of XC95144 : entity is

"0010" & "1001010100001000" & "00001001001" & "1";

attribute USERCODE_REGISTER of XC95144 : entity is

"XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX";

attribute REGISTER_ACCESS of XC95144 : entity is

"BYPASS ( CONLD, HIGHZ )," &

"ISCENABLE[12] ( ISCEN)," &

"ISCONFIGURATION[27] ( FERASE, FBULK, FPGM, FVFY)," &

"ISCDATA[10] ( FPGMI, FVFYI)";

attribute BOUNDARY_CELLS of XC95144 : entity is

" BC_1";

attribute BOUNDARY_LENGTH of XC95144 : entity is 432;

attribute BOUNDARY_REGISTER of XC95144 : entity is

" 0 (BC_1, *, internal, X)," &

" 1 (BC_1, *, internal, X)," &

" 2 (BC_1, *, internal, X)," &

" 3 (BC_1, *, controlr, 0)," &

" 4 (BC_1, PB07_16, output3, X, 3, 0, Z)," &

" 5 (BC_1, PB07_16, input, X)," &

" 6 (BC_1, *, controlr, 0)," &

" 7 (BC_1, PB07_15, output3, X, 6, 0, Z)," &

" 8 (BC_1, PB07_15, input, X)," &

" 9 (BC_1, *, controlr, 0)," &

" 10 (BC_1, PB07_14, output3, X, 9, 0, Z)," &

...省略部分...

end XC95144;

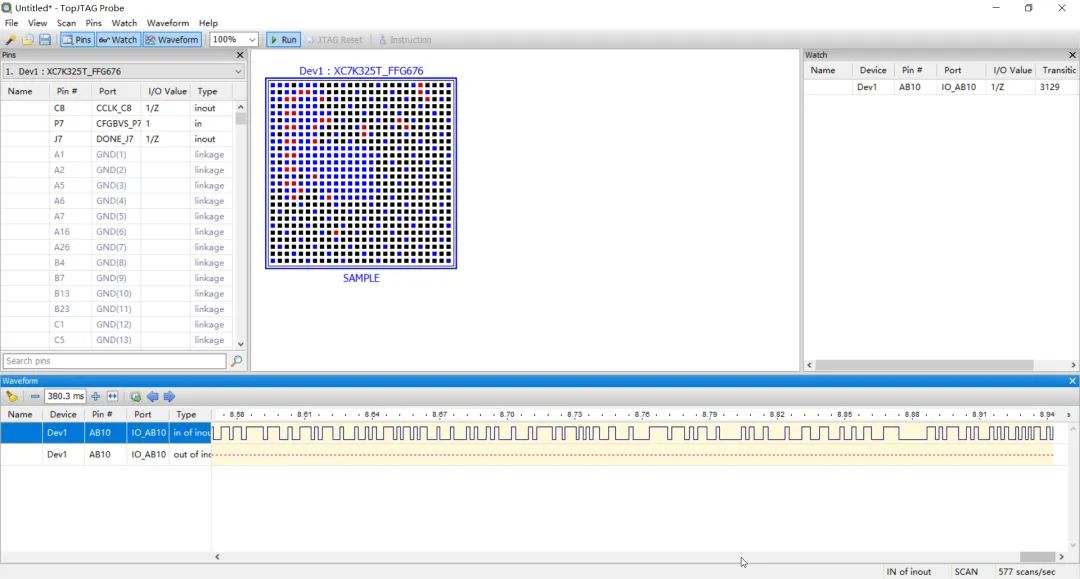

4. Applications of BSDL Files

More Selections

-

Powerful JTAG Boundary Scan 1 – Basic Principles

-

China Mobile Wankou Tiangong Development Board Trial Review

-

Downloading Xilinx FPGA Programs with JLink and OpenOCD

-

Four Methods to Obtain Xilinx FPGA Chip IDCODE (Supports Any FPGA Model)

-

What is Amateur Radio?

-

Xilinx FPGA Multiboot Design and Implementation (Spartan-6 and Kintex-7 Example)