1. Powerful XJTAG

<span>www.xjtag.com/zh-hans/</span>

-

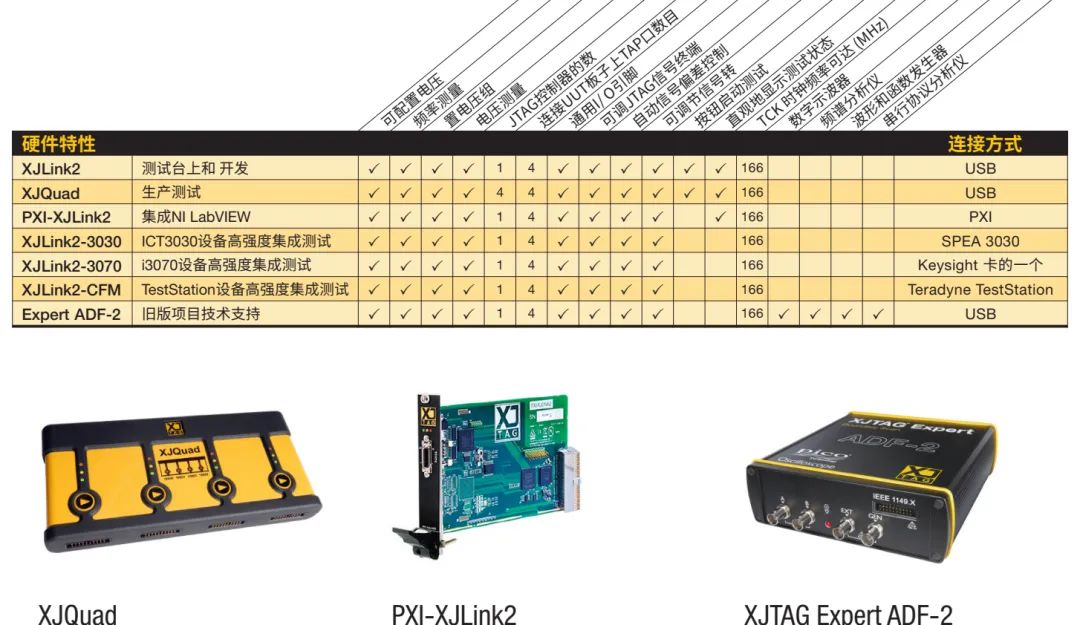

Supports up to 4 TAP interfaces

-

TCK can reach up to 166MHz

-

JTAG signal voltage can be configured, ranging from 1.1 to 3.3V in 0.1V steps

-

All IO pins have built-in voltage measurement and frequency measurement functions

-

Open DLL API interface

2. Compact and Simple TopJTAG

<span>http://www.topjtag.com/</span>-

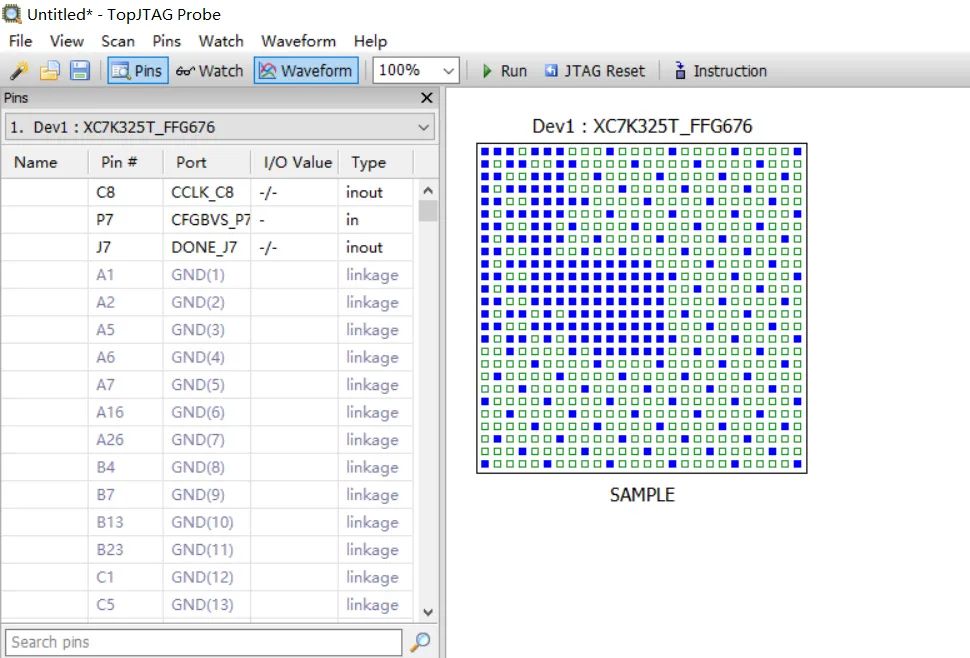

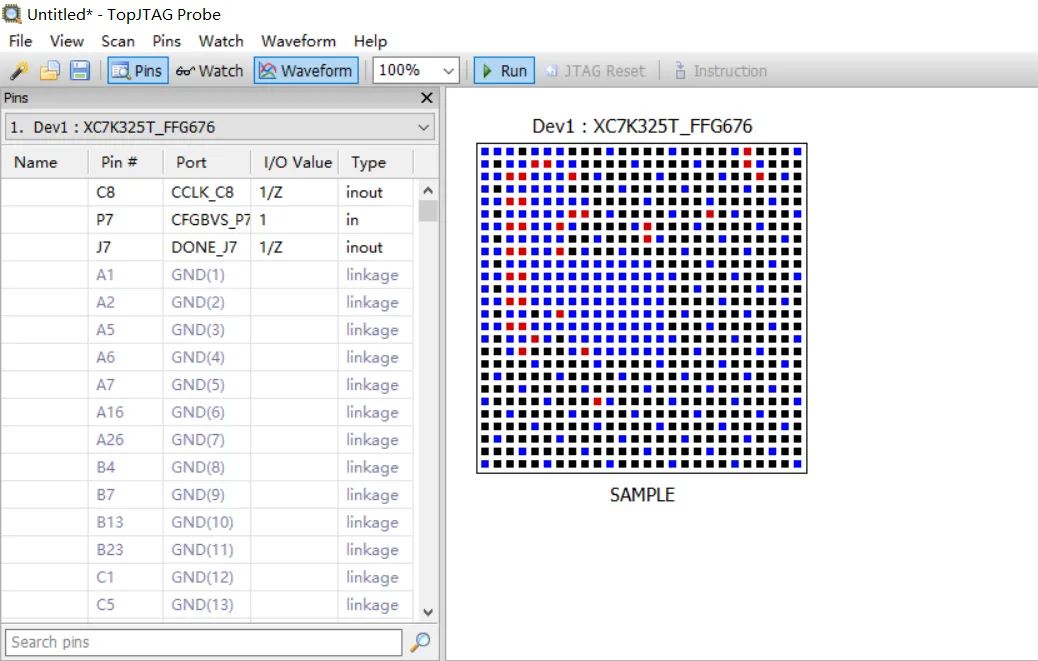

TopJTAG Probe: Boundary scan testing software that can read, control IO, display waveforms, count pulses, etc.

-

TopJTAG Flash Programmer: Can program and read the externally connected CFI Flash chip.

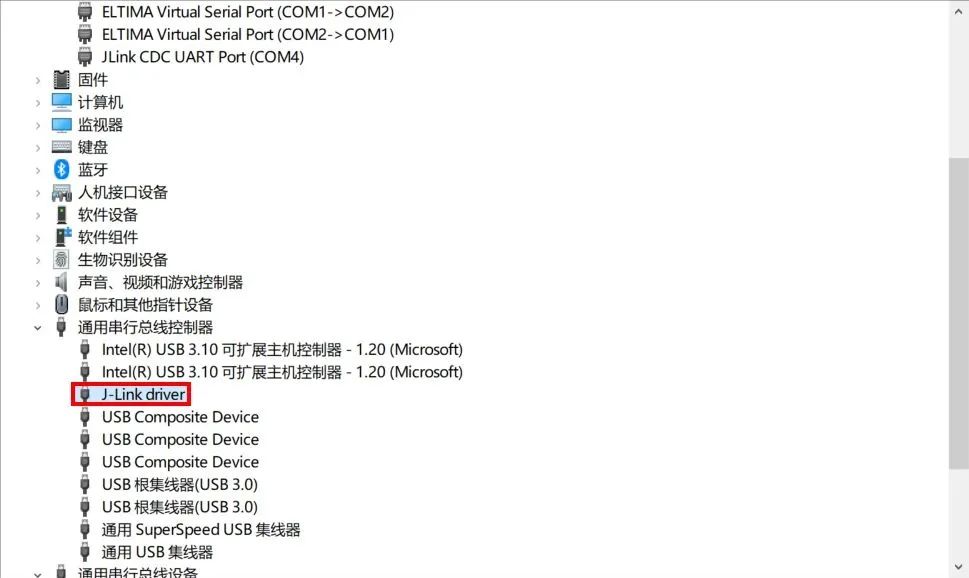

3. Installing TopJTAG

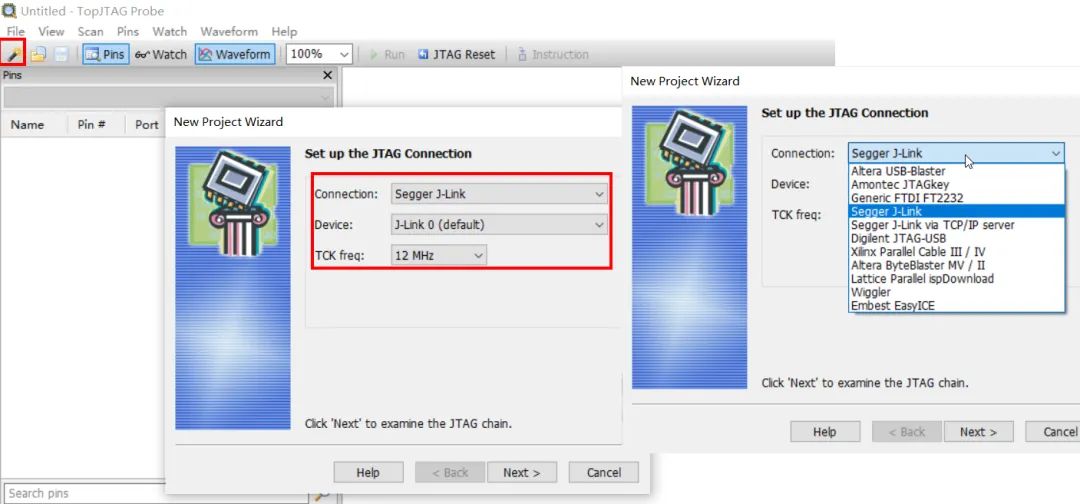

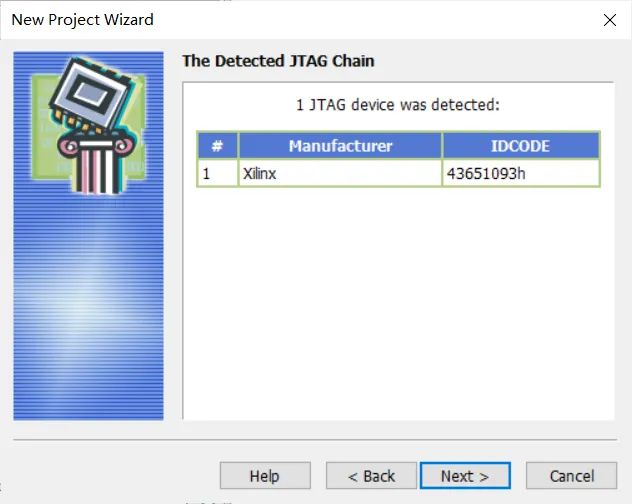

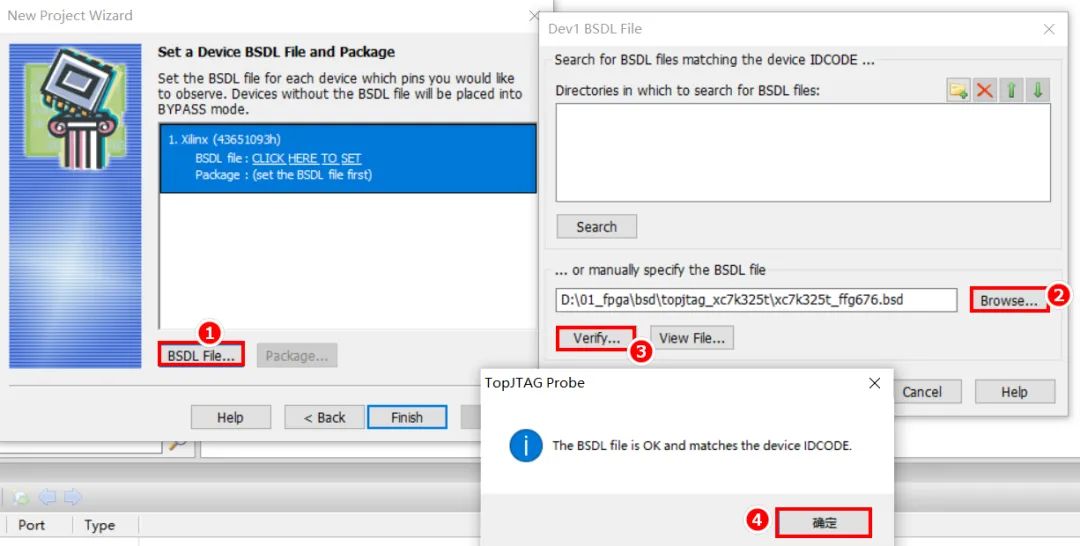

4. Basic Usage of TopJTAG

-

Powerful JTAG Boundary Scan (2): Introduction to BSDL Files.

More Selections

-

Powerful JTAG Boundary Scan 1 – Basic Principles

-

Powerful JTAG Boundary Scan 2 – Introduction to BSDL Files

-

China Mobile Wankou Tiangong Development Board Trial Evaluation

-

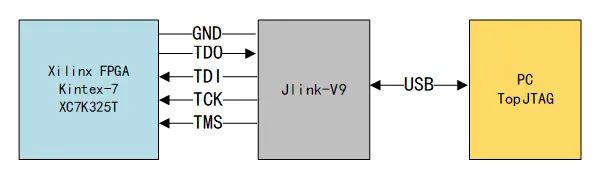

Using JLink and OpenOCD to Download Xilinx FPGA Programs

-

4 Methods to Obtain Xilinx FPGA Chip IDCODE (Supports Any FPGA Model)

-

What is Amateur Radio?

-

Xilinx FPGA Multiboot Design and Implementation (Examples of Spartan-6 and Kintex-7)