Welcome FPGA engineers to join the official WeChat technical group.

Clickthe blue textto follow us

1. What is JTAG: Joint Test Action Group.

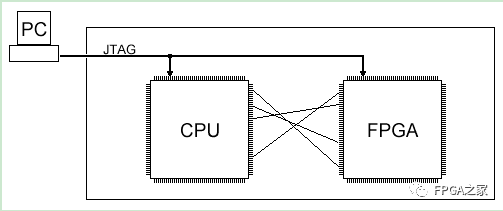

JTAG is an IEEE standard designed to solve board-level issues, developed in the 1980s. Today, JTAG is used for programming, debugging, and probing ports. Of course, the original use was boundary testing.

Boundary Testing:

For example, if you have two chips connected by many wires, how do you ensure that the connections between those wires are okay? You use JTAG, which can control all the IC pins. This is called chip boundary testing. (I have not used this.)

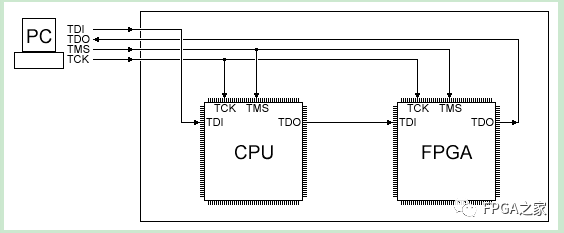

2. JTAG Pins:

JTAG has evolved to have pins, typically four: TDI, TDO, TMS, TCK, and of course a reset pin TRST. The JTAG pins on the chip are actually dedicated.

TDI: Test Data Input, data is input to the JTAG port through TDI;

TDO: Test Data Output, data is output from the JTAG port through TDO;

TMS: Test Mode Select, used to set the JTAG port to a specific test mode;

TCK: Test Clock Input;

TRST: Test Reset;

More amazing uses:

CPU and FPGA manufacturers allow JTAG for port debugging; FPGA vendors allow configuration of FPGA through JTAG, using JTAG signals to enter the FPGA core.

3. How JTAG Works:

The PC controls JTAG: connect the JTAG cable to the PC’s printer port, USB, or network port. The simplest is to connect to the printer port.

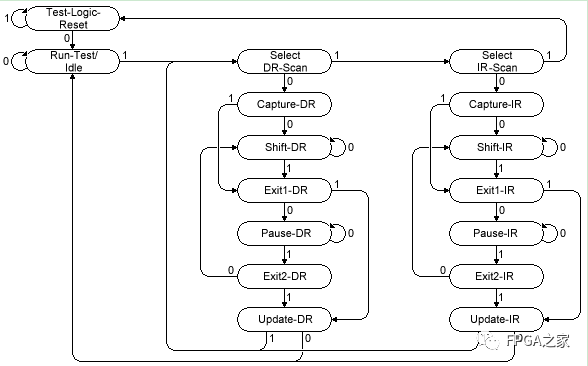

TMS: Inside each chip that has JTAG, there is a JTAG TAP controller. The TAP controller is a state machine with 16 states, and TMS is the control signal for this. When TMS connects all the chips together, the TAP states of all chips transition in unison. Below is a diagram of the TAP controller:

Changing the TMS value will cause the state to transition. If a high level is maintained for 5 cycles, it will jump back to test-logic-reset, usually used to synchronize the TAP controller;

The two most important states are Shift-DR and Shift-IR, both of which connect TDI and TDO.

IR: Instruction Register, you can write values to this register to instruct JTAG to perform a task. Each TAP has only one IR register, and its length is fixed.

DR: The TAP can have multiple DR registers, similar to the IR register, each IR value selects a different DR register. (Very confusing)

4. Questions Related to JTAG Chain:

Calculating the number of ICs in the JTAG chain:

An important application is when the IR value is all ones, indicating the BYPASS command. In BYPASS mode, the DR register in the TAP controller is always a single bit, from input TDI to output TDO, usually one cycle, doing nothing.

You can use BYPASS mode to calculate the number of ICs. If the delay of each IC’s TDI-TDO chain is one clock, we can send some data and detect how long it takes to delay, then we can estimate the number of ICs in the JTAG chain.

Getting the device ID in the JTAG chain:

Most JTAG ICs support the IDCODE command. In the IDCODE command, the DR register will load a 32-bit value representing the device ID. Unlike the BYPASS instruction, there is no standard for the IR value in IDCODE mode. However, every time the TAP controller transitions to the Test-Logic-Reset state, it will enter IDCODE mode and load the IDCODE into DR.

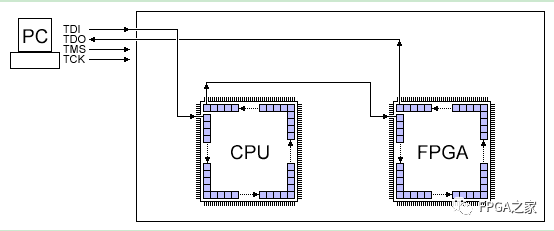

5. Boundary Scan:

When the TAP controller enters boundary scan mode, the DR chain can traverse each IO block or read or intercept each pin.

Using JTAG on FPGA, you can know the status of each pin while the FPGA is running.

You can use the JTAG command SAMPLE, although different ICs may vary.

That’s all.

Welcome communication engineers and FPGA engineers to follow our official account.

FPGA WeChat Technical Group

Welcome everyone to join the national FPGA WeChat technical group, where there is a group of engineers passionate about technology, and here we can exchange and discuss technology together!

Press and hold to join the national FPGA technical group!

FPGA IP core services: various quality IP core service providers, with guaranteed service! If you have needs, you can directly contact the group owner!

FPGA technical group self-operated platform:Xilinx Altera Micron, Samsung, Hynix, ADI TI ST NXP and other brand advantageous agents and distributors, welcome everyone to send model lists whenever needed, we will provide you with the most competitive quotes as soon as possible!Prices are more than 5% lower than your original suppliers! Welcome inquiries – just send your needs to the group owner! We also look forward to you recommending our WeChat to procurement personnel, thank you for supporting the pure technical platform, this way we can continue to improve–

Official thanks to brands in the FPGA technical group: Xilinx, Intel (Altera), Microsemi (Actel), Lattice, Vantis, Quicklogic, Lucent, etc.