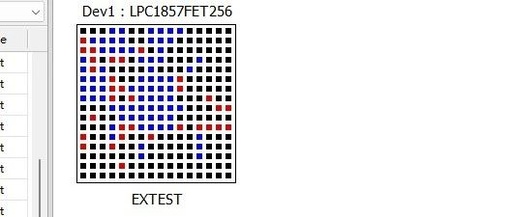

MCU Testing and External NOR Programming Using JTAG_BSDL – LPC1857 Example

1. Introduction Previously, we sharedhttps://mp.weixin.qq.com/s/BeL6UbSg2HI9qKemZugOhw?token=1054074707&lang=zh_CN the article titled“Low-Cost Learning FPGA Based on“Mining Board”” which usesJTAG boundary scan for quick pin correspondence reverse engineering.. Not only forFPGAs, but we can also useJTAG for boundary scan testing inMCUs, provided that the corresponding chip supports this feature and the manufacturer providesBSDL files. Here, we will demonstrate using theLPC1857 … Read more