Research on Fault Injection and Detection Methods for Aero-Engine Electronic Controllers Based on Boundary Scan

Wang Yao, Wen Tiedun, Chen Yaping, Zhang Tianhong

Nanjing University of Aeronautics and Astronautics, School of Energy and Power Engineering

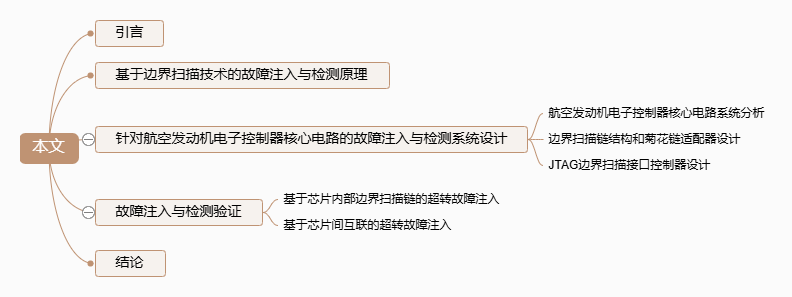

Abstract: The aero-engine electronic controller is a complex circuit system designed around numerous large-scale integrated circuits. Traditional contact-based fault injection and detection methods using physical probes can no longer meet the testability design requirements of such complex circuits. This paper proposes a fault injection and detection method based on boundary scan technology for the core circuits of aero-engine electronic controllers. Based on the analysis of the core circuit, a boundary scan daisy chain and boundary scan controller were designed, capable of performing fault injection and detection based on inter-chip interconnections and internal boundary scan units, validated through the engine overspeed protection logic.

This Paper Highlights

This Paper Highlights

With the continuous development of Full Authority Digital Engine Control (FADEC) technology, the core circuits of aero-engine electronic controllers are gradually becoming denser and more complex. However, traditional contact-based testing methods have become inadequate for the testing needs of modern complex circuits. Efficient and accurate fault injection and detection have become a key challenge in the design and testing of aero-engine electronic controllers.

The research team led by Zhang Tianhong from the School of Energy and Power Engineering at Nanjing University of Aeronautics and Astronautics published a paper titled “Research on Fault Injection and Detection Methods for Aero-Engine Electronic Controllers Based on Boundary Scan” in the 4th issue of Integrated Circuits and Embedded Systems. This paper proposes a fault injection and detection method based on boundary scan technology. Relying on the JTAG interface, the method achieves efficient testing of the core circuits of aero-engine electronic controllers through the design of boundary scan chains and controllers. This research not only provides new ideas for the testability design of complex circuits but also opens new technical paths for the reliability verification of aero-engine electronic controllers.

Limitations of Traditional Testing Methods

The core circuits of modern aero-engine electronic controllers typically contain a large number of high-density surface-mounted components and BGA packaged elements, resulting in a vast number of I/O pins, most of which are interconnected internally. Traditional contact testing methods require test points to be reserved during the design phase, but this approach not only occupies space but also fails to cover all I/O ports. As circuit complexity increases, the testing difficulty and fault injection capabilities of traditional methods are severely limited.

Boundary scan technology provides a new possibility for testing complex circuits as an efficient testing solution. This technology adds shift register units (boundary scan units) near the chip pins, isolating the chip’s input/output pins from internal logic, thus enabling observation and control of pin states. Boundary scan technology not only eliminates the need for additional on-board test circuits but also allows testing to be completed via the JTAG interface, greatly simplifying the testing process.

Fault Injection and Detection Method Based on Boundary Scan

The paper proposes a fault injection and detection method based on boundary scan technology, achieving fault injection and detection through the design of boundary scan daisy chains and controllers. The following are the core technical highlights of this method:

1. Design and Implementation of Boundary Scan Chain

The boundary scan chain is the core structure of this method. By connecting the boundary scan registers of multiple chips in a daisy chain, the pin states of each chip can be accessed. The daisy chain adapter designed in the paper can flexibly connect the scan chain without altering the hardware structure of the prototype verification board, ensuring convenience and universality in testing.

2. Two Methods for Fault Injection and Detection

Based on internal boundary scan units: By directly operating the chip’s boundary scan chain, fault injection can be performed on target pins, and fault detection can be achieved through data shifting in and out.

Based on inter-chip interconnections: By controlling the pin states of the chip, the pin states of other connected chips can be altered, thus achieving fault injection. This method can also be applied to devices that do not have boundary scan structures.

3. JTAG Interface Controller and Host Software

The paper designs a JTAG interface controller based on the CH347 chip and develops corresponding host software. Communicating with the PC via USB, this system can execute boundary scan commands, perform data shifting in and out, and automate fault injection and detection operations.

Experimental Verification: Fault Injection and Detection of Overspeed Protection Logic

To verify the effectiveness of the proposed method, the research team used the overspeed protection logic of the aero-engine electronic controller as the test object, completing fault injection and detection experiments through both the internal boundary scan unit and inter-chip interconnection methods.

Experimental Background

Overspeed faults are serious failures that can occur during the operation of aero-engines, potentially leading to deformation or rupture of rotor components. The overspeed detection function ensures high reliability of the system through a voting signal designed with triple modular redundancy.

Experimental Methods and Results

-

Fault Injection Based on Internal Boundary Scan Units

Fault injection was performed on the triple modular redundant signals through the boundary scan chain, verifying that single-mode signal faults do not change the overspeed flag signal, while dual-mode signal faults lead to changes in the flag signal.

The experimental results indicate that this method can accurately achieve fault injection and detection without requiring additional hardware support.

-

Fault Injection Based on Inter-Chip Interconnections

By altering the pin states of the FPGA chip, fault injection was indirectly performed on the triple modular redundant signals of the ASIC module.

The experimental results show that this method is applicable not only to chips with boundary scan structures but also to devices without boundary scan capabilities for fault injection.

The experimental results of both methods met expectations, validating the feasibility and efficiency of the fault injection and detection method based on boundary scan technology.

Future Prospects

The fault injection and detection method based on boundary scan proposed in this paper provides a new technical path for the testability design of aero-engine electronic controllers. In the future, the research team plans to integrate the boundary scan link and interface controller into the aero-engine electronic controller to achieve built-in self-test (BIST) for complex circuits, further enhancing system reliability and testing efficiency.

Conclusion

As the complexity of aero-engine electronic controllers continues to increase, traditional testing methods have become inadequate. The fault injection and detection method based on boundary scan technology not only efficiently completes the testing of complex circuits but also provides new ideas for the testability design of high-density integrated circuits. This research achievement is of significant importance for advancing the technology of aero-engine electronic controllers and provides valuable references for researchers in related fields.

Citation Format:Wang Yao, Wen Tiedun, Chen Yaping, et al. Research on fault injection and detection methods for aero-engine electronic controllers based on boundary scan[J]. Integrated Circuits and Embedded Systems, 2025, 25(4): 10-19. WANG Y, WEN T D, CHEN Y P, et al. Research on fault injection and detection methods for aero-engine electronic controllers based on boundary scan[J]. Integrated Circuits and Embedded Systems, 2025, 25(4): 10-19 (in Chinese).Previous IssuesIndexListof