DAP, JTAG, and Boundary Scan

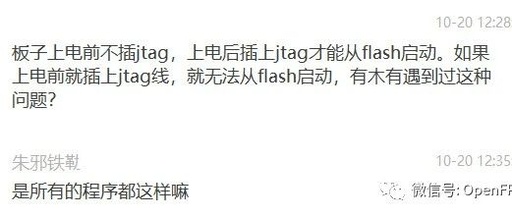

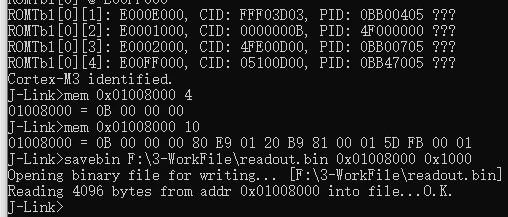

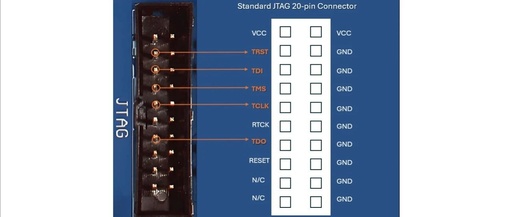

DAP and JTAG There are various ways to connect to the Debug Access Port (DAP), which differ in cost, invasiveness, and security. The DAP allows access to the core within the chip, which is typically the first to boot or is a dedicated microprocessor used for managing chip boot, debugging, and initializing DVFS and DRAM … Read more