JTAG Debugging Standards

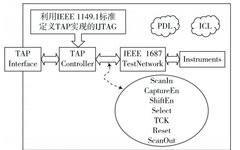

Industry Guiding Standards: Standard Usage and Reference Situations IEEE1149 The JTAG series standard, primarily 1149.1, allows scanning of the JTAG chain on SoCs via the TAP (Test Access Port) interface, enabling command sending and data reading. ARM CoreSight A standardized debug and trace architecture for SoCs defined by ARM. The DAP (Debug Access Port) interface … Read more