FPGA Not Loading Program from Flash When Connected to JTAG Downloader

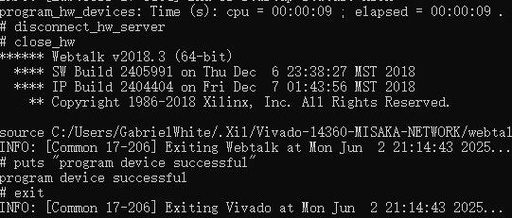

Recently, many people in the group have encountered the above situation, which has been quite puzzling. I had never faced such a situation before. If it were a common issue, there would surely be feedback on the official website. If it is a very specific case, then it can only be treated as a bug. … Read more