Click the “blue text” above to follow for more exciting content.

This article contains a total of 717 words, and reading the full text will take about 2 minutes.

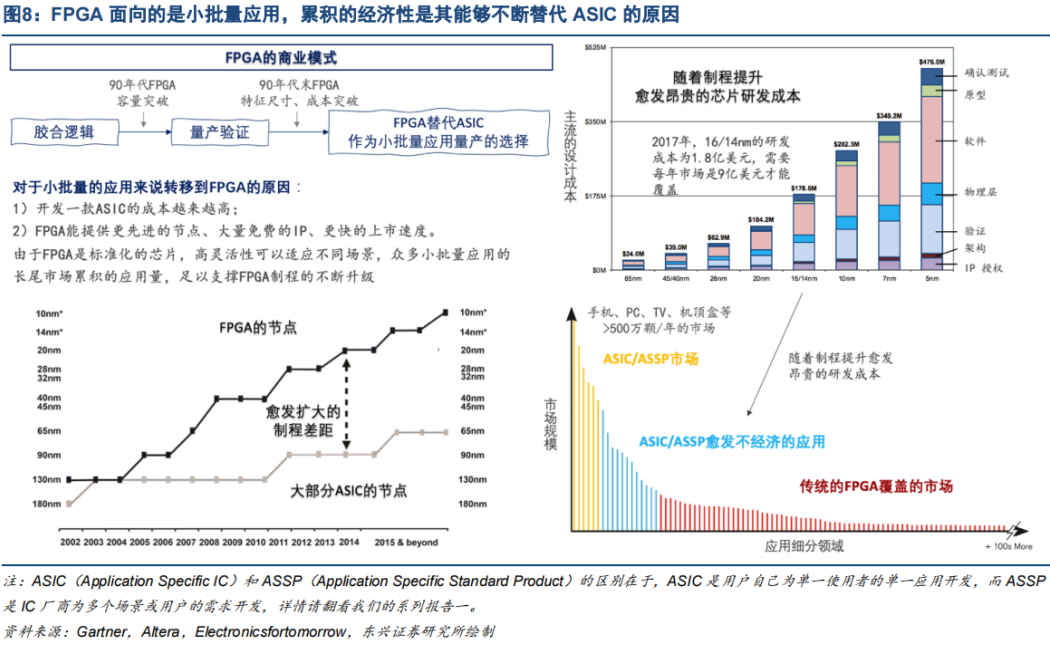

The essence of the FPGA business model is to cover the long-tail market with highly standardized chips to generate economic benefits; the leading companies can maintain a strong monopolistic share because they operate under economies of scale with customer lock-in, allowing them to continuously accumulate advantages through multiple iterations, eroding the market share of other players. In this process, lagging manufacturers are continuously eliminated, and the barriers to entry in the industry are constantly increasing.

The essence of the FPGA business model is to cover the long-tail market with highly standardized chips to generate economic benefits. The accumulated shipment volume from these small-batch applications is sufficient to support the continuous upgrading of FPGA processes. FPGAs are highly standardized chips that can flexibly correspond to different combinational circuits by changing the 16-bit mask in the LUT4 of the FPGA, and combined with registers, they can perform the functions of sequential circuits, thus achieving the “programmability” of any circuit.

This hardware programmability feature allows the same FPGA to implement channel coding functions in 5G base stations and, after reconfiguration, to be used in CNC machine tools for motor control. Therefore, FPGAs are also known as “universal” chips, capable of implementing any circuit design.

In contrast, ASICs/ASSPs are aimed at specific large-scale applications, such as mobile phones, PCs, TVs, and set-top boxes, with annual shipments exceeding 5 million units, or even over 100 million units in some markets. For these large-scale markets, developing a dedicated ASIC/ASSP is sufficient to amortize the upfront R&D costs.

However, as chip processes improve, R&D costs become increasingly expensive, making it less economical to develop an ASIC/ASSP for small-batch applications, leading more customers to turn to FPGAs.

In 2017, the R&D cost for the 16/14nm node was $180 million, often requiring a market of over $900 million annually to cover this cost; developing a 7nm node requires $350 million, with R&D costs and market capacity requirements doubling.

FPGAs can provide nearly the most advanced nodes, with a large number of FPGA manufacturers offering free IP from self-developed or partner sources, providing users with chips that are immediately available, thus accelerating the time-to-market for their products. As more users of ASIC solutions switch to using FPGAs for mass production, the FPGA market has begun to grow rapidly, increasing from $100 million in 1990 to $8.3 billion in 2022.

Risk Warning:This content only represents the analysis, speculation, and judgment of the Breaking Research team, and is published here solely for the purpose of conveying information, not as a basis for specific investment targets. Investment carries risks; please proceed with caution!Copyright Statement:This content is copyrighted by the original party or author. If reproduced, please indicate the source and author, retain the original title and ensure the integrity of the article content, and bear legal responsibilities for copyright and other issues.

END