Click the “blue text” above to follow for more exciting content.

This article contains a total of 2049 words, and reading the full text will take about 5 minutes.

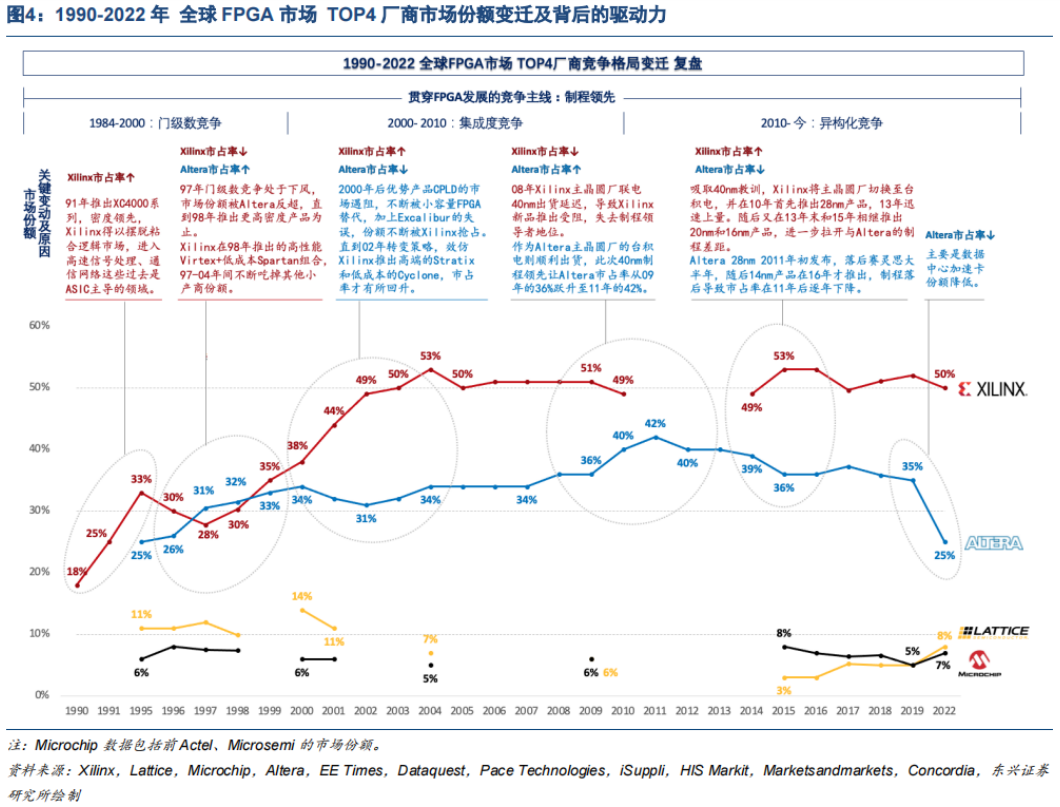

The competition in process technology is the main thread throughout the history of FPGA development, and leading in process technology is the most direct determinant of FPGA market share. The versatility of FPGAs means that their routing and area are not optimal compared to ASICs. Therefore, FPGAs must lead ASICs or ASSPs by several generations in process technology to achieve more competitive performance, making the pursuit of process technology an inevitable choice for FPGAs. Additionally, there is a customer onboarding phase between the release of new products and mass production, during which customers evaluate the newly launched FPGAs from different manufacturers and ultimately decide on one for use in subsequent mass production, completing their circuit design on it, known as a Design-win, which typically takes 9-12 months. Due to the differences in development environments and product architectures, once a decision is made, it is very difficult and time-consuming for users to switch to another FPGA supplier. This high level of binding creates a strong barrier for FPGAs, allowing the first players to launch products to often capture a large portion of the market share. Generally, design-wins in the latest process technology can predict market share in the FPGA market 2-3 years later and enjoy a certain advantage in the next round of process competition, as customers typically do not easily change suppliers. Xilinx, the leading FPGA manufacturer, has historically been a leader in process technology, maintaining a market share of around 50% since 2003, with only Altera able to keep pace with Xilinx, while other industry players lag behind by 2-3 generations.

In addition to the ongoing competition in process technology, different stages of FPGA development have different competitive focuses, which are essentially the performance and technological breakthroughs at various stages of FPGA:

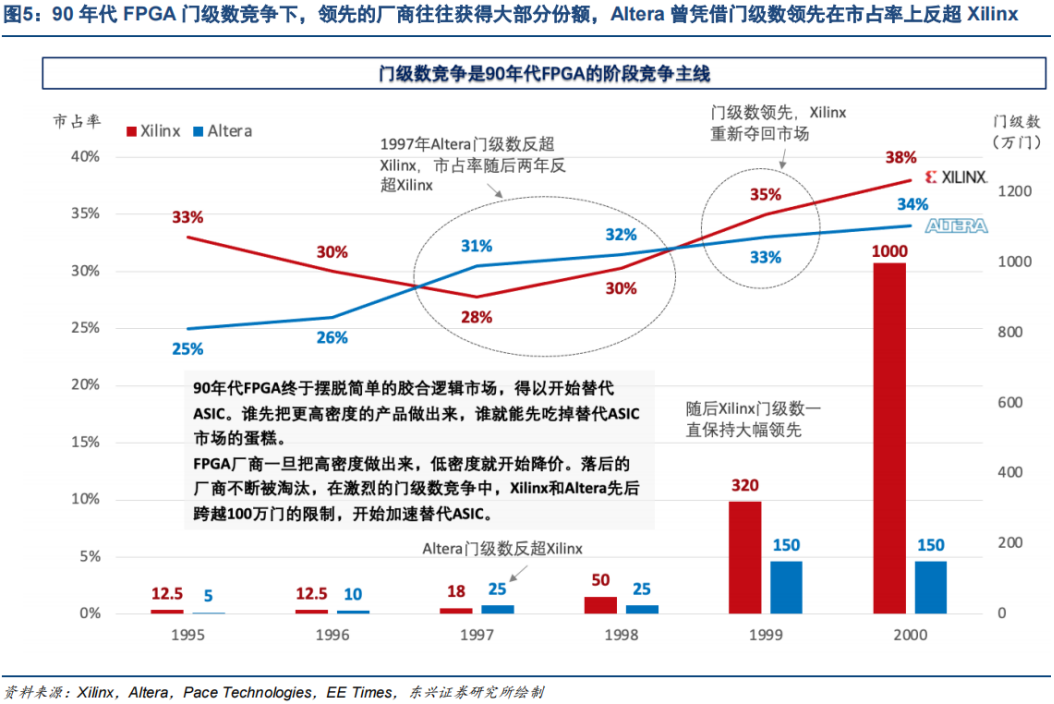

The competition in gate count was the primary competitive focus for FPGA manufacturers in the first stage (1984-2000). The demand for performance improvement behind the replacement of ASICs meant that the leader in gate count often captured most of the market share. In the 1990s, complex electronic systems required millions of gates, mostly implemented using standard cells and gate arrays. In the early 1990s, the capacity of FPGAs was only 200,000 to 500,000 gates, and although they had moved away from the glued logic market, they still could not enter the higher-end ASIC market. Consequently, throughout the 1990s, FPGA manufacturers competed on gate count, with whoever could produce higher density products first able to capture the market share from ASIC replacements. Through improvements in architecture such as the number of LUT inputs, cluster structure, and interconnect forms, coupled with the push of Moore’s Law, the density and speed of FPGAs rapidly increased. Once FPGA manufacturers produced higher density products, lower density products began to drop significantly in price, leading to the elimination of lagging manufacturers. In the fierce competition for gate count, Xilinx and Altera both surpassed the 1 million gate limit in 1998-1999, accelerating the replacement of gate arrays, standard cells, and ASICs, and continuously increasing their market share.

During this stage, FPGA competitors engaged in intense patent wars to defend their competitive advantages in high-density architecture and EDA.

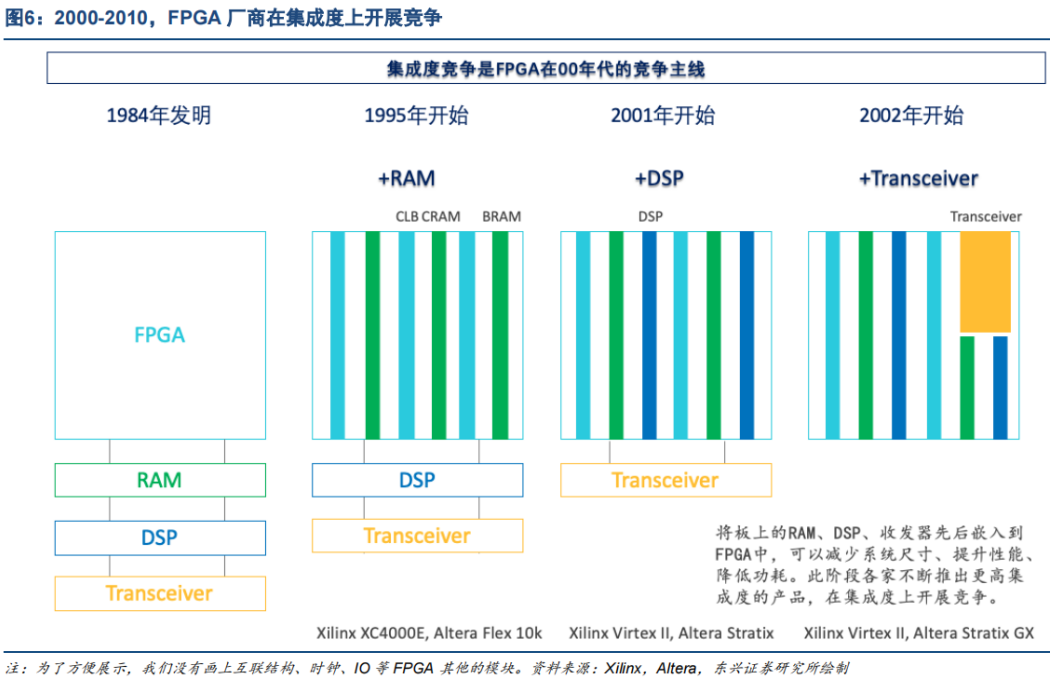

The competition in integration was the primary competitive focus for FPGA manufacturers in the second stage (2000-2010). Integrating discrete components such as DSP onto the FPGA was driven by the need to reduce circuit area, lower power consumption, and system costs, with manufacturers that launched high-integration FPGAs first capturing more market share from competing products like DSP. In the mid-1990s, FPGA manufacturers discovered that users frequently used LUTs as storage (i.e., “soft” implementation), which occupied many logic units, leading to insufficient FPGA capacity. Therefore, RAM was the first unit to be integrated into FPGAs. Solidifying these frequently used functions into FPGAs could greatly enhance computational efficiency, and users would not have to worry about wasting precious logic resources, while also reducing routing, pins, and pads on the board, thereby decreasing PCB area and power consumption. For example, embedding DSP into FPGAs (instead of implementing it through universal LUTs and registers) could save 80% of the power and the area occupied by discrete DSP on the board. Thus, after surpassing gate count in the late 1990s, FPGA manufacturers shifted their competitive focus from gate count to integration, embedding RAM, DSP, transceivers, and other units that originally belonged on the board into FPGAs to reduce customer power consumption and total system costs, further encroaching on the market of other discrete components. Altera’s FLEX 10K was the first FPGA to integrate RAM, and Xilinx acquired Rocketchip in 2000 to gain high-speed transceiver capabilities, embedding transceivers in the Virtex II Pro released in March 2002.

However, having more integrated units on a single FPGA does not necessarily mean better performance. Except for the highest-end customers, many customers often only need specific integrated units. Therefore, FPGA manufacturers began to differentiate their product lines, with Xilinx launching high-end Virtex and low-cost Spartan lines, where Virtex targeted the complex communication equipment market, and Spartan and CPLD Coolrunner targeted the consumer electronics market. Among them, Virtex also differentiated into multiple product series, such as in Virtex 4, where the LX series is the highest-end FPGA for large, high-density communication applications, while the SX series is rich in DSP resources for replacing discrete DSP devices, and the FX series includes high-speed serial connections. Altera also launched high-end Stratix and low-cost Cyclone in 2002, with Stratix further differentiating into a series that includes high-speed transceivers. It is evident that the competition in integration reflects the competition in product definition, showcasing the ability of FPGA manufacturers to communicate and understand customer needs.

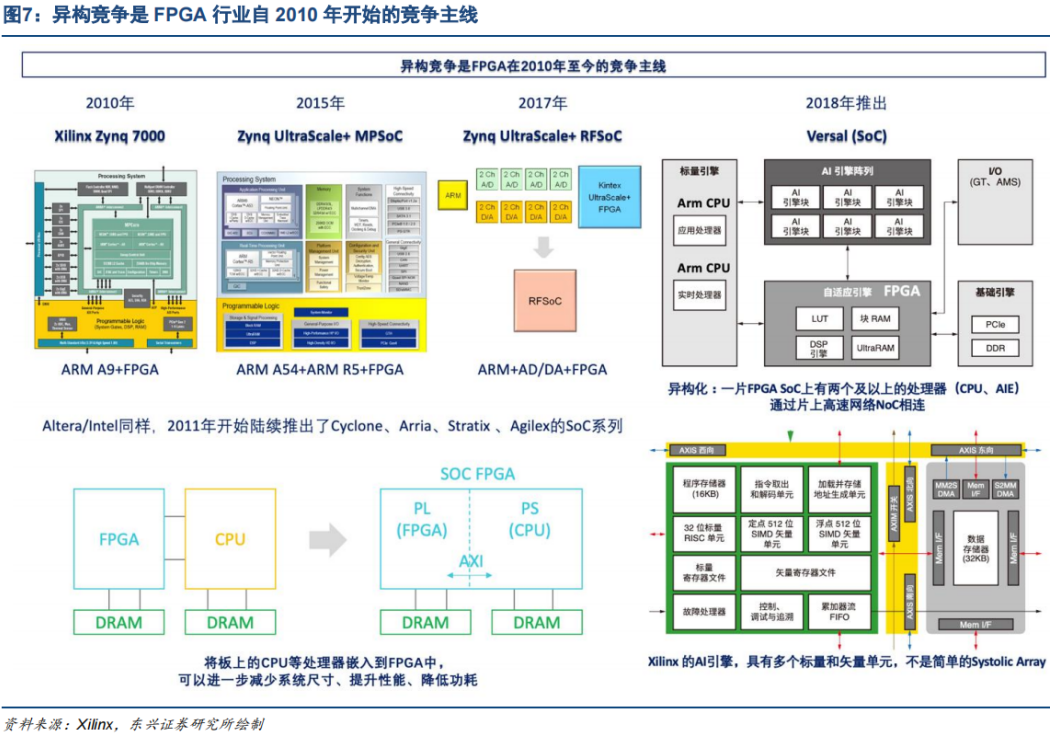

The competition in heterogeneity is the current competitive focus for FPGA manufacturers (2010-present). FPGA manufacturers are competing to launch SoC FPGAs by embedding CPUs and other processors onto FPGAs, continuously capturing market share from embedded processing. As routing shifts from PCB to on-chip, processing delays are shorter, resulting in higher overall performance, and further reducing board area and power consumption, allowing SoCs to possess both the flexibility of CPUs and the high parallel computing capabilities of FPGAs. For example, Xilinx’s RFSoC integrates ARM + 4 ADCs + 4 DACs + 1 Kintex UltraScale+ FPGA, reducing area by 50%, power consumption by 30%-40%, and costs by 40%-60% compared to discrete solutions, with latency reduced by 80%-90% compared to JESD204. Since Xilinx launched the Zynq 7000 in 2010, FPGAs have entered the era of heterogeneous competition, further capturing the market originally using discrete FPGA + CPU solutions. In Xilinx’s Zynq series, communication between PL (FPGA) and PS (ARM CPU) is done via the AXI bus. Xilinx subsequently launched the Zynq MPSoC for high-definition video processing and RFSoC for wireless communication. Currently, Xilinx’s Zynq series SoC FPGAs are widely adopted in industrial, multimedia processing, communication, and medical applications, with the latest series being the 7nm ACAP Versal family, which integrates CPUs and Xilinx’s AI engines, with units connected via a high-speed NoC. Altera/Intel has also successively launched Cyclone, Arria, Stratix, and Agilex SoC FPGAs since 2011, covering low-cost, cost-effective, and high-end scenarios.

Risk Warning:This content only represents the analysis, speculation, and judgment of the Breaking Research team, and is published here solely for the purpose of conveying information, not as a basis for specific investment targets. Investment carries risks; please proceed with caution!Copyright Statement:This content is copyrighted by the original party or author. If reproduced, please indicate the source and author, retain the original title and ensure the integrity of the article content, and bear legal responsibilities for copyright and other issues.

END