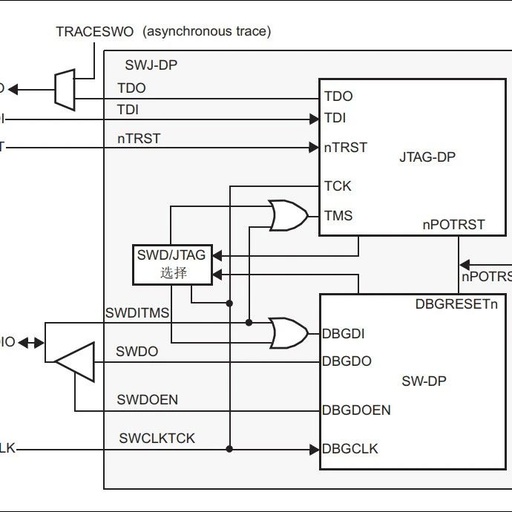

SWD Low-Level Implementation Principles

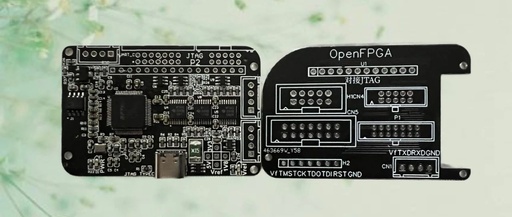

Author | strongerHuang WeChat Official Account | Embedded Column The mainstream download interfaces for microcontrollers based on the Cortex-M core are JTAG and SWD. Differences Between SWD and JTAG Pins: JTAG: TDI:Test Data In. Serial input pin TDO:Test Data Out, serial output pin TCK:Test Clock, clock pin TMS:Test Mode Select, mode select (control signal) pin … Read more