Skip to content

WeChat Official Account | Embedded Column

The mainstream download interfaces for microcontrollers based on the Cortex-M core are JTAG and SWD.

Differences Between SWD and JTAG Pins:

-

TDI:Test Data In. Serial input pin

-

TDO:Test Data Out, serial output pin

-

TCK:Test Clock, clock pin

-

TMS:Test Mode Select, mode select (control signal) pin

-

TRST:Test Reset, reset pin

-

SWDIO:Serial Wire Data Input Output, serial data input output pin

-

SWCLK:Serial Wire Clock, serial wire clock pin

SWD only requires two lines (SWCLK and SWDIO), making it a good choice when PCB layout is limited and pin resources are tight.

SWD: Serial Wire Debug, represents serial wire debugging, is a protocol designed by ARM for programming and debugging its microcontrollers.

There are many downloaders on the market that support the SWD debugging interface, such as:ST-Link, J-Link, e-Link, GD-Link, and most downloaders used for Cortex-M core processors support it.

For SWDIO, it is a bidirectional (input/output) data pin, and a pull-up must be applied to the circuit board (ARM recommends using 100K).

Every time the direction of SWDIO is changed in the protocol, a transition time is inserted, during which the line is neither driven by the host nor the target. By default, this transition time is one bit time, but it can be adjusted by configuring the SWCLK frequency.

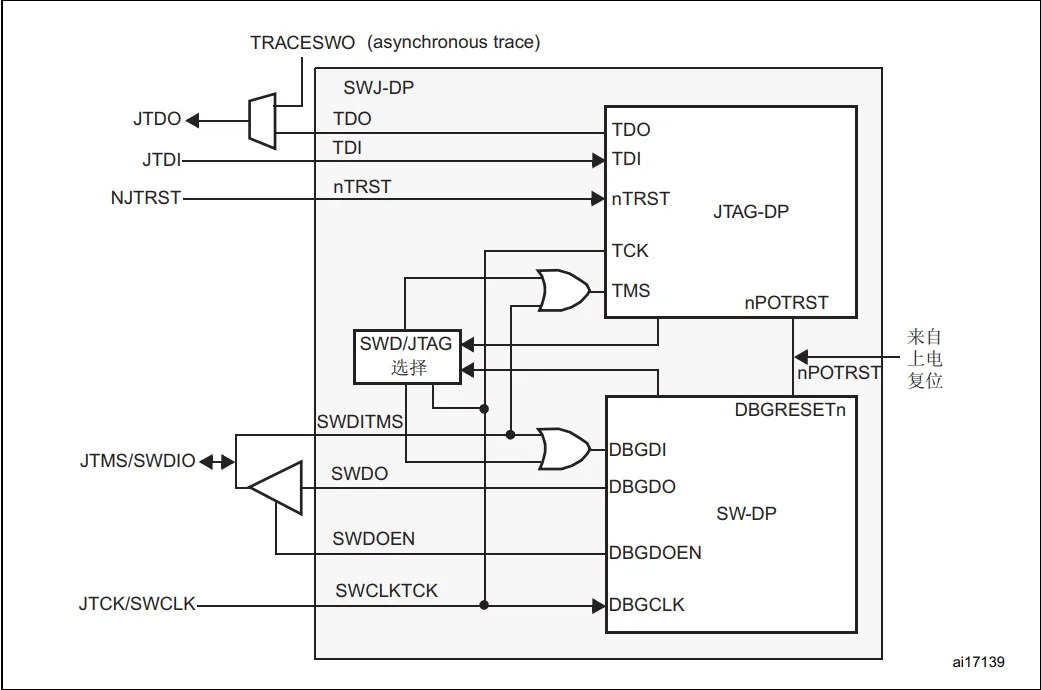

Common Cortex-M core processors integrateSWD and JTAG debug ports, where two JTAG pins of SW-DP are multiplexed with five JTAG pins of JTAG-DP in SWJ-DP.

Switching Mechanism Between JTAG and SWD:

The default debug interface is the JTAG interface. If the debugging tool wants to switch to SW-DP, it must provide a dedicated JTAG sequence on TMS/TCK (mapped to SWDIO and SWCLK respectively) to disable JTAG-DP and enable SW-DP. This allows SWDP to be activated using only the SWCLK and SWDIO pins.

1. Output TMS (SWDIO) = 1 signal for more than 50 TCK cycles

2. Output 16 TMS (SWDIO) signals 0111100111100111 (MSB)

3. Output TMS (SWDIO) = 1 signal for more than 50 TCK cycles

Each sequence consists of three stages:

-

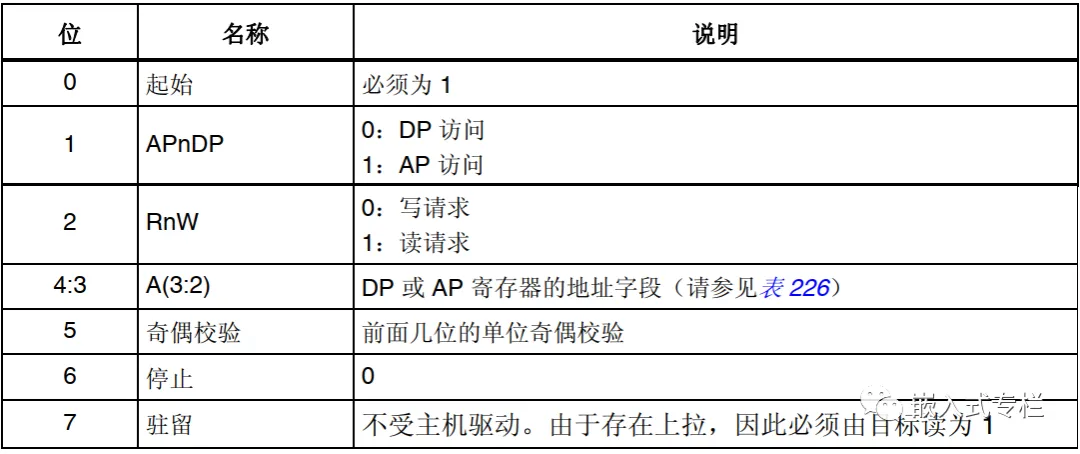

The host sends a data packet request (8 bits)

-

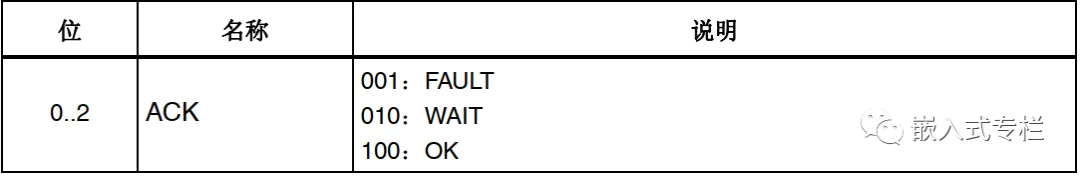

The target sends a confirmation response (3 bits)

-

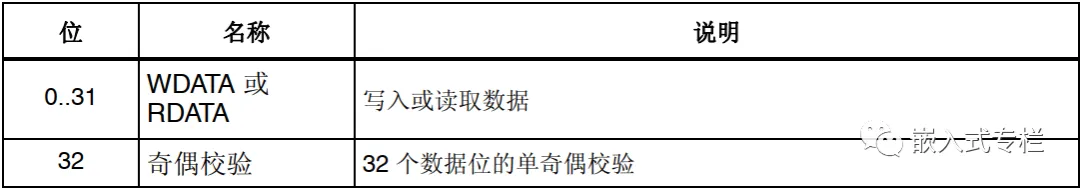

The host or target sends the data transfer stage (33 bits)

Data Packet Request (8 bits):

This is similar to some bit operations of registers, and the underlying principles have similarities withcommon communication protocols.

The state machine of SW-DP has an internal ID code to identify SW-DP, including main states: reset, idle state, ID code, etc.

-

After power-on reset, after switching DP from JTAG to SWD, or if the line is high for more than 50 cycles, the SW-DP state machine is in the reset state.

-

If the line is low for at least two cycles after the reset state, the SW-DP state machine is in the idle state.

-

After the reset state, the state machine must first enter the idle state before performing a read access to the DP-SW ID CODE register. Otherwise, the target will issue a FAULT confirmation response on another transaction.

For more details on the SW-DP state machine, refer tosome manuals related to Cortex-M.

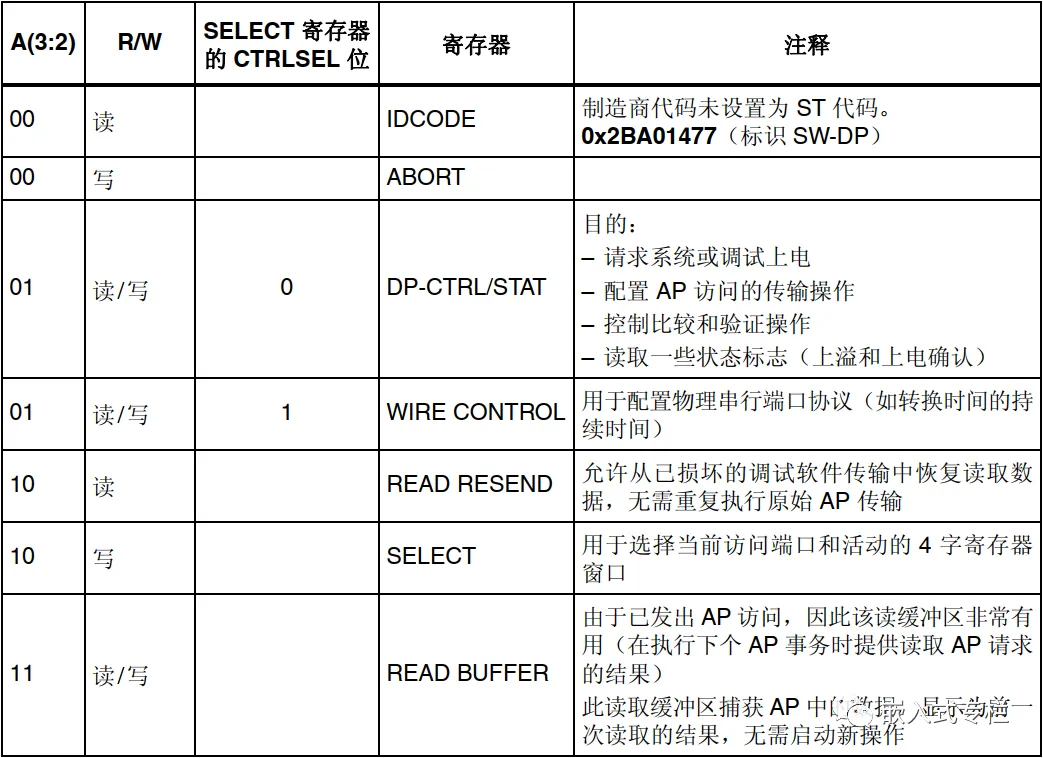

SWD is similar to ordinary peripherals and has a type of register. The programming (read/write) operations performed by developers are actually operations on the corresponding registers.

This concludes the introduction to the underlying principles of SWD. For more details, please refer toCortex-M core manuals.