Low-Power Design: Retention Cell

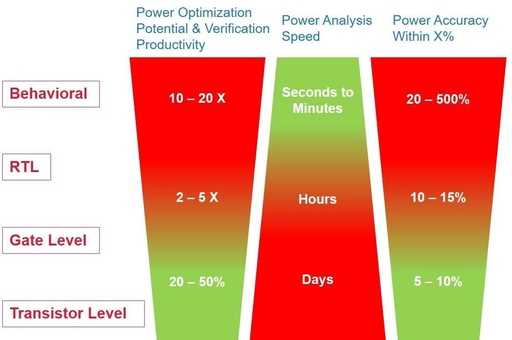

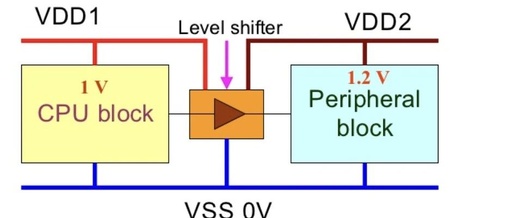

Low power design has always been a top priority in chip design. The low power technologies adopted by Jingxin SoC training camp include: 1. Clk gating, turning off the clock signals of non-working modules; 2. Power gating, turning off the power of non-working modules; Power gating is more power-efficient than Clk gating because it eliminates … Read more