~ Reply the following keywords to see more IC design tutorials ~

Currently supportedkeywords include:

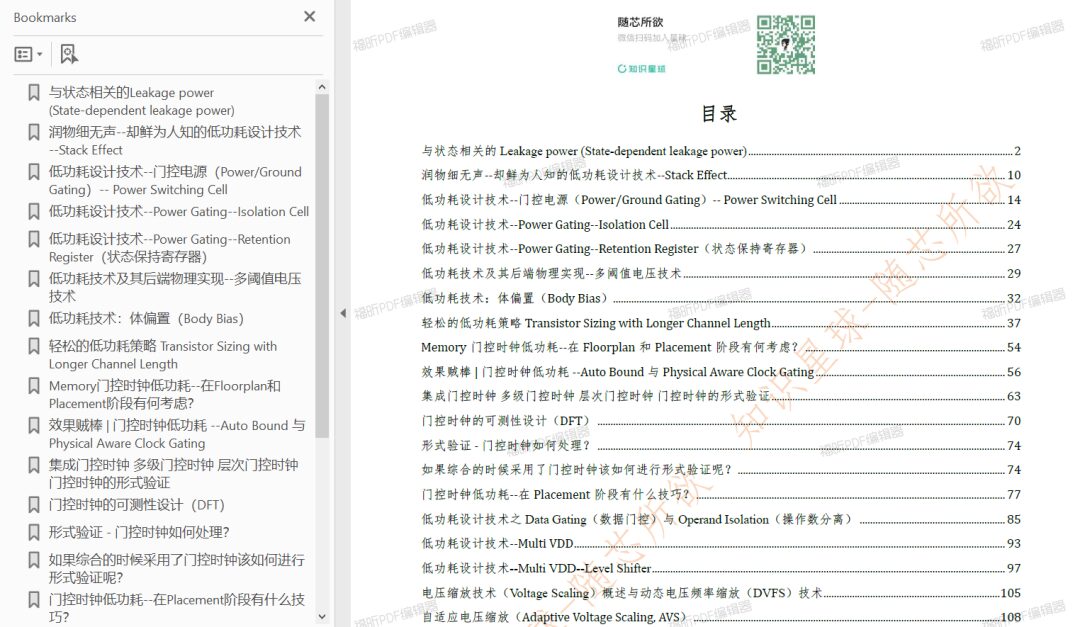

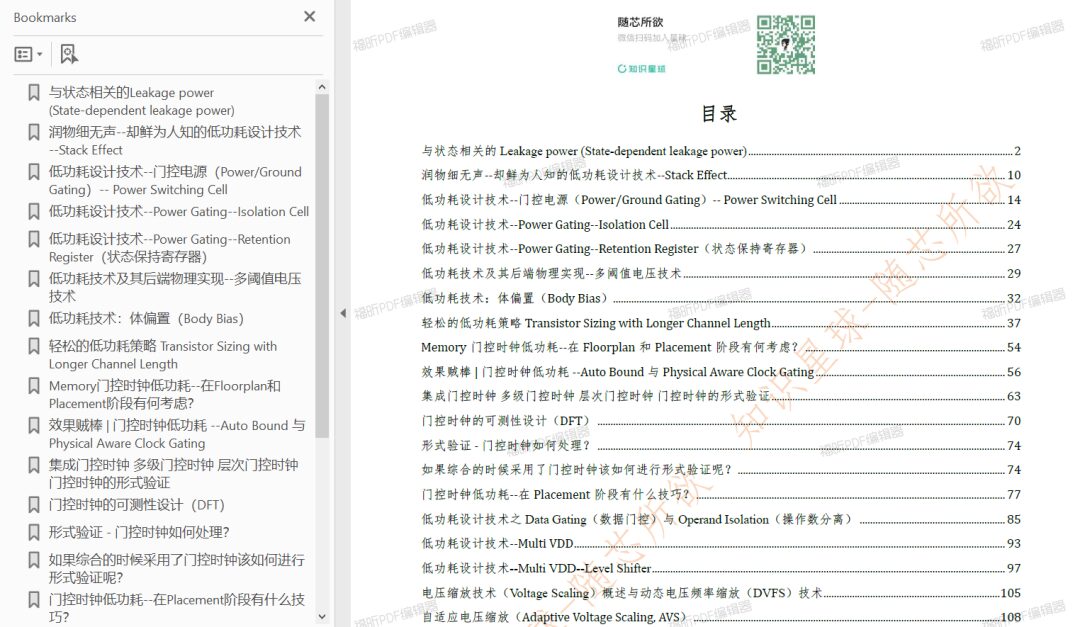

Innovus ICC or IC Compiler

DC or Design Compiler PT or PrimeTime

Low power design has always been an important aspect of digital IC design and is a significant knowledge point in many company interviews and exams. Therefore, Knowledge Planet has compiled a comprehensive《Low Power Design Techniques Summary》 (accumulated notes over 7-8 years, totaling 30,000 words, 129 pages, richly illustrated, with a directory and tags for easy reference), which is absolutely essential for backend design. You are welcome to join the planet to view more complete and comprehensive low power design content (QR code at the end of the article). Additionally, the planet also includes exciting topics such asIR-drop, Timing and more.

Below are the low power series articles previously published on the public account:

Overview of Low Power Design Methods:

Low Power Design Techniques

Digital Backend Low Power — Various Low Power Techniques and Their Applications in IC Backend Layout

Register Transfer Level Low Power Design Techniques:

Low Power Design Strategies — State Machine Encoding and Decoding

Low Power Design Strategies — Resource Sharing

Low Power Design Strategies — Binary Number Representation

Techniques to Reduce Static Power:

State-dependent Leakage Power

Subtle yet little-known low power design technique — Stack Effect

Low Power Design Techniques — Power Gating — Power Switching Cell

Low Power Design Techniques — Power Gating — Isolation Cell

Low Power Design Techniques — Power Gating — Retention Register

3. Multi-threshold Voltage CMOS Circuit

Low Power Techniques and Their Physical Implementation — Multi-threshold Voltage Technology

Low Power Technique: Body Bias

5. Transistor Sizing with Longer Channel Length

Easy Low Power Strategy | Transistor Sizing with Longer Channel Length

Techniques to Reduce Dynamic Power:

Well-known low power technique | Clock Gating (CG) technology

Looking back — The history of Integrated Clock Gating Technology — Separated Clock Gating Technology

Memory Clock Gating Low Power — What considerations are there in the Floorplan and Placement stages?

Amazing Effects | Clock Gating Low Power — Auto Bound and Physical Aware Clock Gating

Integrated Clock Gating, Multi-level Clock Gating, Hierarchical Clock Gating, Formal Verification of Clock Gating

Testability Design of Clock Gating (DFT)

Formal Verification – How does Clock Gating handle?

Clock Gating Low Power — What tips are there in the Placement stage?

XOR Self-Gating and Design Compiler Topo Implementation | Sending Netease Cloud Course Coupons

Low Power Design Techniques of Data Gating and Operand Isolation

3. Multi VDD Circuit Technology

Low Power Design Techniques — Multi VDD

Low Power Design Techniques — Multi VDD — Level Shifter

4. Dynamic Voltage Frequency Scaling (DVFS)

Overview of Voltage Scaling Techniques and Dynamic Voltage Frequency Scaling (DVFS)

Adaptive Voltage Scaling (AVS)

5. Multi-bit Flip-flop (MBFF)

Low Power Design Techniques — Multi-Bit Flip-Flop (MBFF) Technology

UPF CPF:

UPF and Low Power Design Implementation Example — Including UPF and DC Synthesis Script

CPF Application Example

PTPX Low Power Analysis Related:

PTPX Power Analysis Tutorial-1 Including Averaged Power Analysis Script

PTPX Power Analysis Tutorial-2 Including Time-Based Power Analysis Script

How to view PTPX generated power waveform files using nWave

Knowledge Planet mainly shares tutorials related to digital IC backend (both text and video). If interested, you can join us, guiding you from a novice to a backend expert, with an annual salary of a million not being a dream.

Highlights of Knowledge Planet

Planet Benefits – PV/Calibredrv and Virtuoso Video Tutorial Collection

-

-

A wealth of IC backend design insights

-

Student Guide, Lab, Lab Guide, and Process Library Sharing

-

IC Backend Tutorials, Interview and Exam Experiences Sharing

-

IC Design Video Tutorials

-

ICC2/ICC Innovus Calibredrv PT and other EDA Software Tutorial Sharing

-

Synthesis/PR/PV/IR/EM/ECO and other tutorial sharing

-

All paid articles from the public account can be viewed for free on the planet

-

Helping you solve doubts and questions

-

8% discount on Netease Cloud Classroom courses