Looking at today’s applications, whether in the Internet of Things, consumer mobile devices, or various devices that can connect to wall outlets, including servers, low power consumption has become a differentiating factor and a necessary condition for product success (as noted by techsugar).

Written by: Brian Bailey

Translated by: Editorial Team

Advancements in mobile technology have led the industry to pay attention to power consumption issues, but now it is necessary to assess the total energy consumed by each task within the system. Every unnecessary action taken by the system while executing specific tasks wastes energy, and developers need to adopt new methods and architectures to reduce energy waste.

More and more practitioners are beginning to focus on power consumption issues. “Mobile system-on-chips (SoCs) have led the emphasis on power consumption,” said Rob Knoth, Director of Product Management at Cadence. “Looking at today’s applications, whether in the Internet of Things, consumer mobile devices, or various devices that can connect to wall outlets, including servers, low power consumption has become a differentiating factor and a necessary condition for product success (as noted by techsugar).”

Whether it is a highly complex large system or a portable small device, power consumption is given high priority. At the server level, addressing complexity and power consumption issues is a driving force for technological development. “Artificial intelligence is causing the size of SoCs to expand rapidly,” said Jay Roy, Director of SoC Power Continuity at Synopsys. “Tech companies like Amazon and Facebook, which are heavily investing in AI technology, find that cooling solutions are increasingly dominating costs, so engineers at these companies must intensify their research into power consumption.”

Portable devices are another extreme, with some devices needing to save every joule of energy. “Battery-free low-power Bluetooth (BLE) products are very suitable for low data rate applications,” said Srinivas Pattamata, Vice President of Business at Atmosic Technologies. “In many IoT applications, Bluetooth connections are the most power-hungry part of the system. However, IoT applications often require small batteries to support years of sensing and data processing, so tens of milliwatts of power consumption is already too high.”

There is one point on power consumption that everyone has reached a consensus on. “Wasted power is an important term,” said Preeti Gupta, Director of Register Transfer Level (RTL) Products at ANSYS. “AMD defined this term, which means that the power supply must do work, and the energy consumed during idle periods is wasted power.”

How is this concept different from before? “Power is an instantaneous concept, while energy is the accumulation of actual work over time,” said Knoth from Cadence. “Whether it’s battery life, system architecture, or completing a specific task more efficiently, energy is a better quantifiable analysis metric. Energy analysis requires the use of more complex functional stimuli, power analysis, and various optimization techniques.”

Traditional Technology

Energy design requires continuous attention and cannot be optimized in isolation at any time. “During development, the concept of power consumption varies at different stages,” Roy from Synopsys pointed out. “It’s not just the hardware team that needs to focus on power consumption; the software team or the entire SoC team must also pay attention, as they will ultimately focus on the same thing: how to achieve the lowest power consumption.”

Power consumption optimization already has mature solutions in certain directions. “Power consumption mainly consists of three parts: leakage current, short-circuit power, and switching power,” Gupta from ANSYS said. “Engineers have optimization methods for these three directions. However, new challenges have emerged, such as glitch power, which has become increasingly significant in certain types of designs, especially those containing a large number of XOR gates. Therefore, DSPs or algorithm-heavy applications will encounter glitch power issues. Developers can control the circuit’s capacitance, voltage, and frequency to reduce power consumption, such as adjusting voltage to lower supply voltage, using multiple power domains, or using gated circuits for on-demand power supply; in terms of frequency, there are dynamic frequency adjustment techniques and methods to turn off clocks for non-working parts using gated circuits. Many low-power technologies have already become routine tools for developers, spanning the entire product development phase, from algorithm concepts to final mass production. Developers need to do extensive work to reduce power consumption, such as multi-power optimization, pin swapping, or path balancing.”

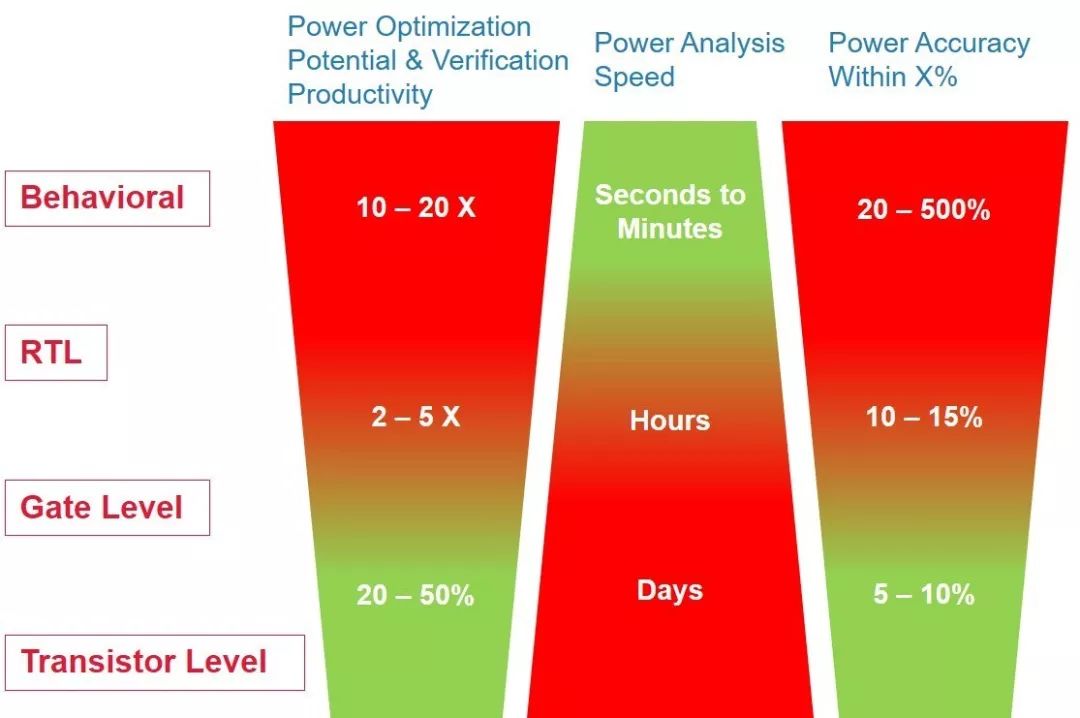

Power Analysis and Optimization Across Different Abstraction Levels

Source: Cadence

Every step of the development design process affects power consumption. “At the layout stage, about 5% to 10% of power consumption optimization can be achieved,” Knoth said. “Going back, about 20% of power consumption optimization occurs during the synthesis stage, from RTL to gate-level circuit stage; moving further up, about 80% of power consumption optimization happens at the architecture design stage, such as determining data paths, multicore parallel computing algorithms, and dynamically lowering frequencies to reduce power consumption for certain tasks, etc.”

Going Further

Thirty years ago, functional verification was still done by directly looking at waveforms. “Now, if you look at waveforms cycle by cycle, how efficient can the verification be?” Knoth asked. “If it’s not fast, nothing can be done. It’s similar in low-power design; development teams need more precise quantifiable analysis methods, repeatedly checking throughout the entire development process and using regression testing and other techniques.”

Many definitions of development processes are still in their early stages. “Mastering any concept cannot be separated from existing tools and methodologies,” Roy said, noting that these technologies and methodologies include simulation, virtual prototyping, and matching vector sets.

Why is simulation important? “Simulation allows developers to delve into the entire SoC and provides scalability, enabling real scenario simulations,” Roy continued. “Ten years ago, it wasn’t possible to do what we can now; in the past, it was enough to complete functional verification, but now we need to assess power consumption through simulation. Software is crucial because the software running on the chip has a huge impact on power consumption, and the interaction between software and hardware is gradually becoming a focus.”

Qazi Ahmed, Product Marketing Manager at Mentor, a Siemens Business, provided examples to demonstrate the growing importance of software-hardware interaction. “Automotive electronics, machine learning, and AI applications require a lot of memory access operations. By performing statistical analysis on these operations, we can map the most frequently accessed memory operations to a small memory, partition memory into different regions, or use register read/write to replace some memory operations. These techniques can significantly reduce power consumption, sometimes reducing dynamic memory power consumption by 30%.”

Sometimes, virtual prototypes can be used for analysis. Virtual prototypes provide more precise analysis than existing technologies. Knoth said, “Many people are still using spreadsheets to analyze power consumption, and the results are mainly based on guesses. Virtual prototypes bring the greatest benefits to power consumption analysis, followed by optimization based on High-Level Synthesis (HLS).”

This analysis method is increasingly recognized in the industry. Roy said, “They can build SystemC models or ISS models for key components, allowing us to discuss on this basis and providing more room at the architecture level to reduce power consumption. To make the analysis more effective, the underlying engine for estimating power consumption needs to be reasonably correlated.”

Significant progress has been made in power consumption analysis at the high-level synthesis stage, and the rapid development of IoT and edge devices has made this trend increasingly evident. The demand for technological development has expanded the application of high-level synthesis to power consumption analysis, allowing for parameter trade-offs from a high-level perspective of the system.

Max Odendahl, CEO of Silexica, said, “Developers want to increase system data throughput while reducing area and ultimately lowering power consumption, and power consumption interacts with throughput and area. We have discussed centralized computing for a long time; to achieve the performance required for centralized computing, a centralized computing architecture must be adopted, but this architecture wastes a lot of energy from the numerous power supply batteries in centralized computing.”

The Biggest Difference

The essential difference between power and energy is vectors. “If the process is made more sensitive to power consumption, functional stimuli are needed,” Knoth said. “However, developers often do not fully understand the quality and characterization of stimuli when they add some stimuli. Engineers traditionally conduct static analysis, which is very useful for optimizing power consumption, but if engineers can transition from static analysis to functional vector analysis, it means they have shifted from power consumption analysis to energy analysis.”

This requires changes in team structure. “The specific functional activities of the chip have a first-order impact on power consumption, but chip companies typically have the verification team responsible for building functional application activity scenarios, while the power design methodology team is responsible for running simulations using power analysis tools and using the simulation results to advise chip design engineers on how to modify designs to reduce power consumption. As a result, designers do not receive the complete information needed for comprehensive power design. Some companies have changed the functions of their power design methodology teams, allowing them to be responsible for both power verification and simulation work to reduce fragmentation in the process.”

The scale of chip functional verification can be quite large. Jay Roy from Synopsys said, “Functionality depends on software application scenarios, and the previous execution platforms were not scalable, so they could not analyze real power consumption levels. But now it is different; past power analysis tools could only analyze modules for 10,000 to 20,000 cycles, while current tools can analyze the entire SoC, examining functional activities over billions of cycles. The next generation of platforms for true SoC-level power consumption analysis must be scalable and capable of handling large systems and designs.”

How functional activities of the chip affect design tools is illustrated by Knoth’s example of mapping: “During synthesis, there is a description (elaboration) step, a mapping step, and then different optimizations involving gate circuits and routing are processed. In the mapping phase, designers need to select multiplier or adder architectures from the high-level detailed version of RTL, and functional stimuli assist in power consumption optimization. Automated tools help engineers make the right choices during synthesis, which indeed helps reduce the overall energy consumption of the product. The development process has undergone significant changes; in the past, power and area requirements were met first, and then power consumption was considered. Now, power consumption is a core factor in product cost estimation, and performing power consumption analysis earlier allows for correct choices to be made early in development.”

However, this approach also carries potential risks. For instance, the scenarios used in simulations may not cover all actual application scenarios, leading to over-optimization in some cases and potentially failing to predict worst-case scenarios.

Strategy Formation

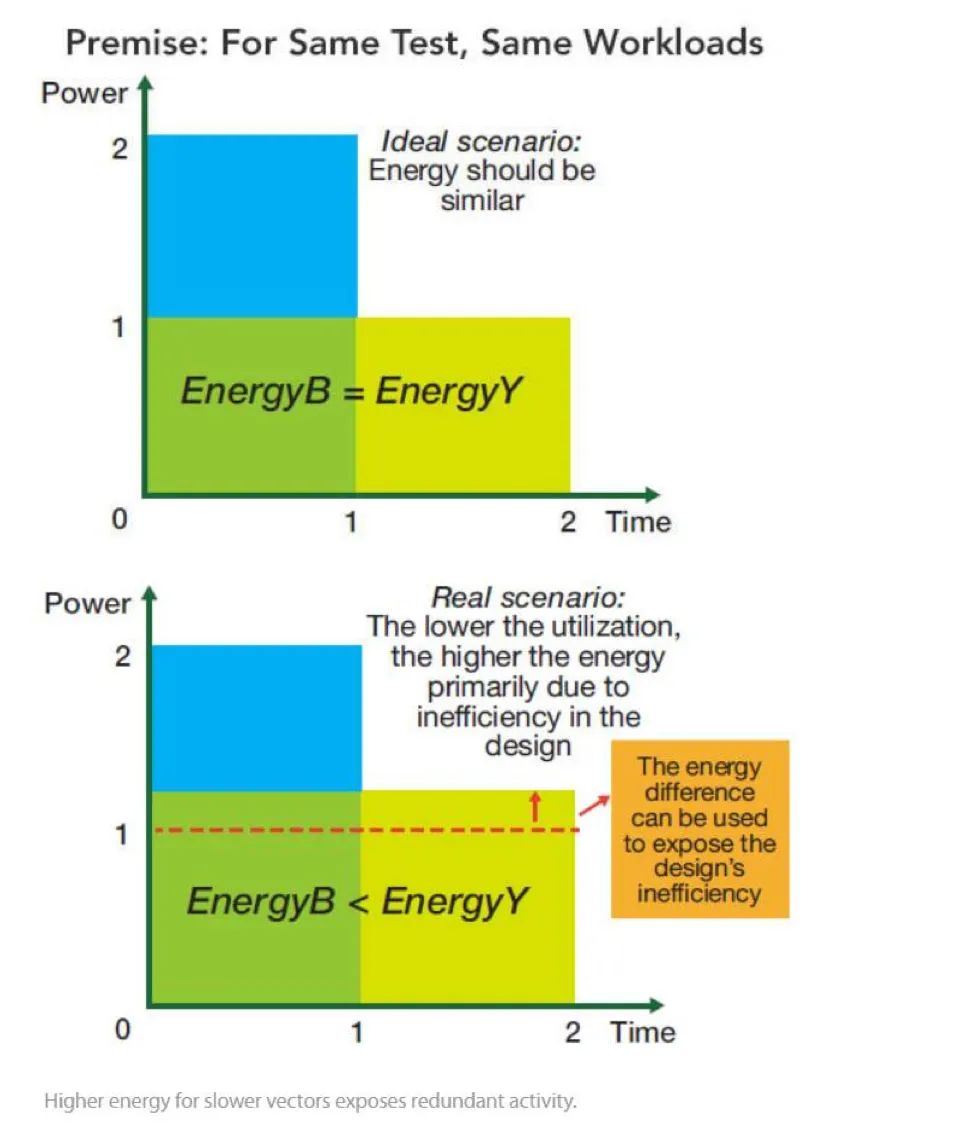

Many companies still adhere to their initial design methodologies. Gupta introduced a strategy adopted by Qualcomm’s GPU team for identifying power loss, stating, “Completing a certain function consumes a certain amount of energy, whether it is done in t time or 2t time, the energy consumed should be the same; power is different because power equals energy divided by time. If more time is needed to complete a function, then power will decrease, while the total energy to complete that function remains unchanged. However, if it is detected that the energy to complete a function varies with time, then there may be an issue with power supply efficiency in the system.”

Another strategy is to utilize more sequential analysis in design. Ahmed from Mentor explained, “Companies can perform sequential analysis to check whether the outputs of a group of flip-flops are observable or stable under certain conditions. This allows tools to generate more robust expressions for these flip-flops, thereby reducing dynamic power consumption in CPU/GPU designs by 5% to 10%. In networking and communication designs, power consumption reductions can exceed 50% in some cases. Memory has similar fine-grained gating conditions known as memory gating, which can save more than 25% of dynamic memory power consumption. The inputs for data processing can also be gated, known as operand isolation, which can save 5% to 10% of dynamic power consumption. Unused switches on memory inputs can be turned off to save power, even if it is minimal.”

This analysis also exists at higher levels. Roy said, “Considering data flow across module boundaries, if I have a data-producing module and several data-consuming modules, you might find that the data-producing module is very active. However, if the data-consuming modules are idle, it is best to stop the transmission. There is still much room for exploration regarding cross-IP interactions related to functional activities.”

Conclusion

Change takes time. Gupta warned, “Scenarios are crucial for power consumption analysis; failing to understand this will be the biggest mistake for development teams. This is not only for measuring power but also for developing high-energy-efficient designs. If a system will be idle 90% of the time, design optimization needs to be targeted toward that condition. This has not been well understood.”

Power and energy run through all aspects of system development. Development teams must work together to address power consumption issues, as no single person or just part of an organization can complete the power design task alone; both design and verification teams are equally important. Each stage of development must have a reasonable division of labor to conduct corresponding analysis and optimization. However, vector generation has traditionally been the task of the verification team. Now, every stage of chip development must provide corresponding vector sets to achieve comprehensive optimization of the system.

This article is translated from the semiengineering website, author: Brian Bailey

END