Click the “blue text” above to follow for more exciting content.

This article contains a total of 1567 words, and reading the full text will take about 4 minutes.

How do FPGAs lock in customers? Since the most critical layout and routing can only be performed in the FPGA vendor’s own EDA, the software and hardware of FPGAs are strongly bound. The high switching costs make it very easy to lock in customers, leading to stable demand throughout the entire lifecycle. FPGA vendors will begin sample testing for customers as soon as they release prototypes of the next generation of products, allowing customers to choose among several FPGA suppliers. Once the selection is completed, the FPGA vendor achieves a “design-win” because the customer needs to complete their circuit design on the FPGA and will not switch suppliers. Implementing circuits on FPGAs is critically dependent on layout and routing. The reason FPGAs can bind customers is that the layout and routing can only be completed in the corresponding FPGA vendor’s own EDA, creating a strong binding between software and hardware. Furthermore, due to the differences in details and EDA environments among different FPGA vendors, switching to another FPGA vendor is very difficult. The larger the design, the more challenging the transition becomes, typically requiring a complete re-run of the “synthesis-layout-routing” process, accompanied by extensive debugging work, and adapting to new FPGA platforms can often take nearly six months. Therefore, unless necessary, customers usually do not switch FPGA vendors but instead repeat orders annually based on their mass production plans, demonstrating very strong customer stickiness. This results in significant scale effects for leading players in customer acquisition, and stable customers further consolidate market share.

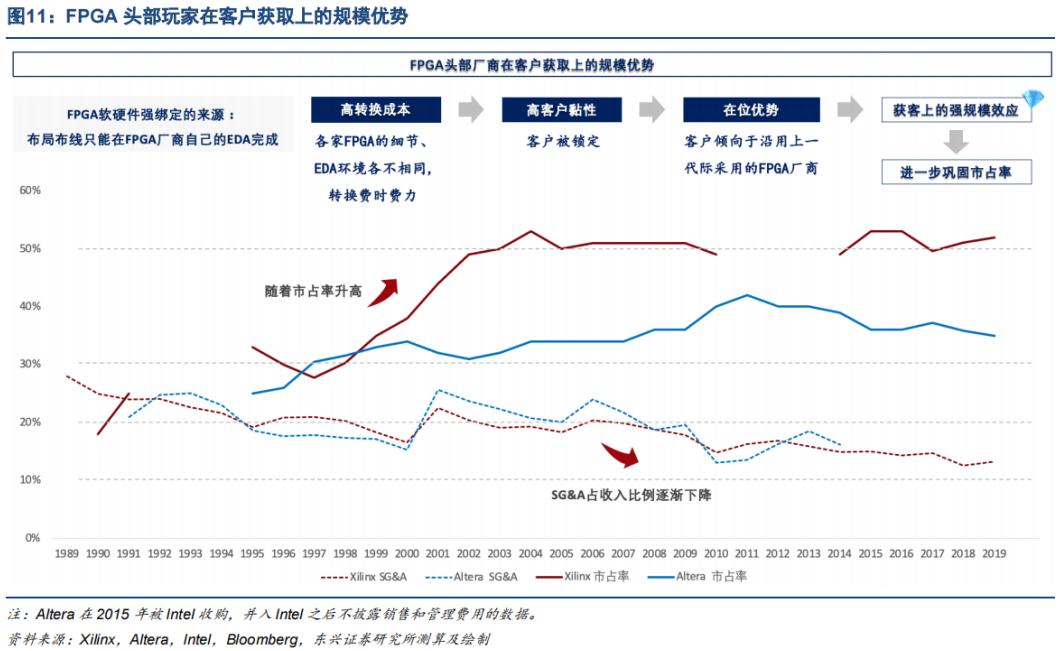

High customer stickiness leads to economies of scale in customer acquisition costs for leading FPGA players, further raising the industry’s entry barriers. Similarly, to reduce switching costs, customers tend to continue using the previous generation of FPGA suppliers, indicating that inter-generational customer stickiness is also very strong, which allows leading FPGA manufacturers to achieve economies of scale in customer acquisition costs. As Xilinx’s market share rose from 19% in 1990 to 50% in 2003, its SG&A (selling and administrative expenses) as a percentage of revenue fell from nearly 30% to 20%, and over the 20 years after Xilinx consolidated its market position, it gradually decreased to nearly 10%. Altera also saw its SG&A ratio drop from a peak of 25% in the 1990s to 16% in 2014, fully demonstrating the scale advantages of leading players in customer acquisition.

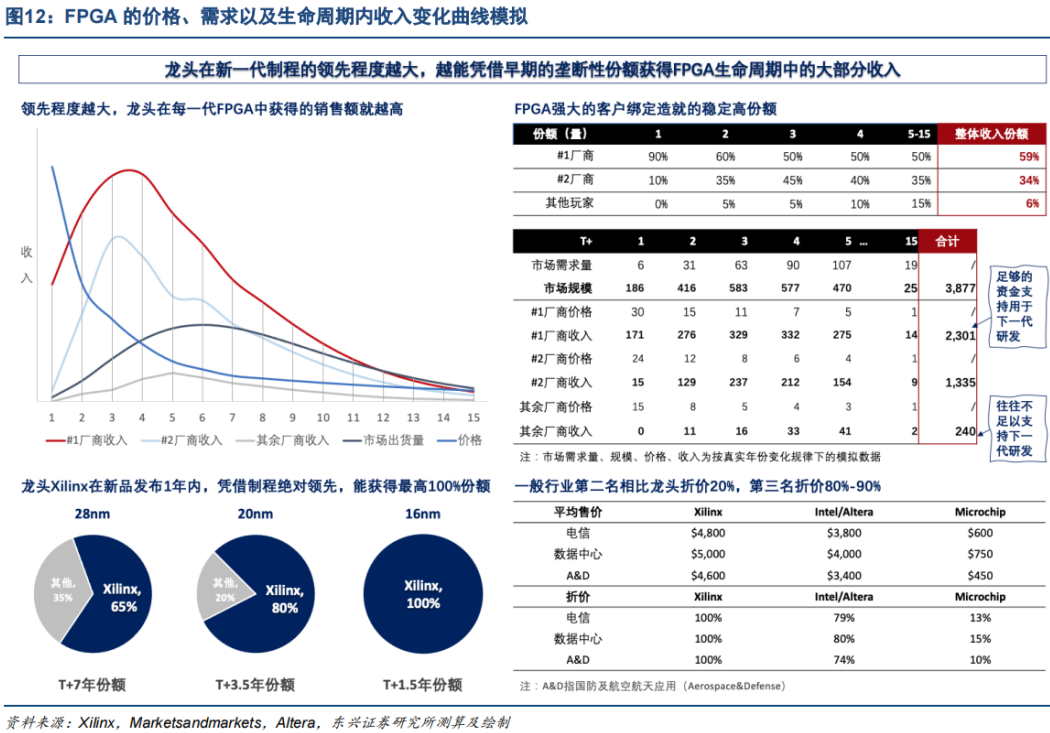

Therefore, for FPGA vendors, the competitive strategy is to launch the next generation of products as early as possible, completing as many design-wins as possible in the first two years to lock in more customers. Since the selection process typically lasts 9-12 months, if a vendor can launch a new product more than half a year ahead of its competitors, customers usually have no choice but to design using that vendor’s products and begin mass production 1-2 years later, allowing the leading vendor to capture 100% of the early market share. This is why the leading process technology for FPGAs can often predict market share two years into the future. For example, Xilinx released its 16nm UltraScale+ product in September 2015, while its competitor Altera did not release its 14nm Stratix 10 until October 2016, more than a year behind Xilinx, resulting in Xilinx achieving 100% market share for the new generation of products by June 2017.

After securing strong design-wins, FPGA vendors can quickly reduce costs through large orders in the HVM (High-Volume Manufacture) phase and further initiate aggressive price reductions to prevent latecomers from entering the market. Once customers complete their selection, they begin their system design, and after finalizing samples for downstream customers, they start placing large production orders with FPGA vendors, typically completing the selection to system design within two years. Once the HVM phase begins, FPGA vendors can quickly amortize the initial investments, including NRE and software development fixed costs, and start aggressive price reductions. For instance, Xilinx reduces prices by 30% annually after launching new products, totaling a 50% reduction over two years. Therefore, FPGA vendors that are more than two years behind in process technology often face very strong entry barriers. It is estimated that even if they start capturing 15% of market demand in the fifth year, their cumulative revenue over the entire historical cycle would only account for 6% of the overall market, often insufficient to support the development of the next generation of new products. In contrast, leading vendors can capture 59% of the revenue from this generation of FPGAs over their entire lifecycle, which is sufficient for the development of the next generation of products. In other words, lagging vendors will fall further behind, and the number of competitors for the next generation of products will decrease. This is also why many players historically have not survived beyond five years; lagging vendors cannot generate enough revenue to invest in the high costs of developing the next generation of products and choose to exit. After 2-3 iterations, the proportion of other players in the market significantly decreases, and market share concentrates towards the leaders.

Risk Warning:This content only represents the analysis, speculation, and judgment of the Breakthrough Research, and is published here solely for the purpose of conveying information, not as a basis for specific investment targets. Investment involves risks; please proceed with caution!Copyright Statement:This content is copyrighted by the original party or author. If reproduced, please indicate the source and author, retain the original title and ensure the integrity of the article content, and bear legal responsibilities for copyright and other issues.

END