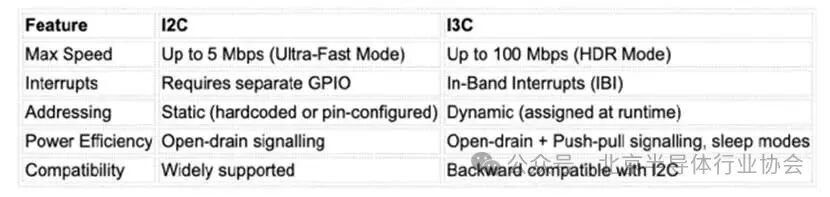

(Source: Chip Interfaces ApS)Invented by Philips Semiconductors (now NXP Semiconductors) in 1980, the I2C (Inter-Integrated Circuit) bus made significant strides in simplifying communication in embedded systems. It is a simple two-wire interface used for synchronous, multi-master/multi-slave, single-ended serial communication.Forty-five years later, it is still widely used to connect low-speed peripheral integrated circuits (ICs), processors, and microcontrollers. However, the silicon landscape has changed; we have evolved from 8-bit MCUs to multi-core SoCs, and from simple sensors to complex multi-mode sensor devices. The demands for bandwidth, latency, and power consumption are increasing, which has paved the way for the development of new improved bus variants.What is I3C and why is it important?I3C (Improved Inter-Integrated Circuit) is a bus developed by the MIPI Alliance, which is a two-wire interface based on I2C, enhanced to improve speed and efficiency. It is designed to replace I2C (and partially SPI) while maintaining backward compatibility with I2C. It offers higher clock speeds of up to 12.5 MHz, in-band interrupts without additional lines, dynamic addressing, dual data rates, and multi-channel operation (up to 100 Mbps), energy-saving modes, and a standardized command set. It is a faster, more streamlined successor designed specifically for modern embedded systems and is rapidly becoming the default choice for SoC and FPGA designers.Why transition to I3C? A comparison of I2C and I3C.The success of I2C is attributed to its simple one data line (SDA) and one clock line (SCL) architecture, allowing up to 127 devices on the bus. It does not require chip select for each device like SPI, making it an ideal choice for low pin count packages and simplified PCB routing. As technology has advanced, SoCs have become increasingly complex, and time-sensitive designers have begun to reach the limits of I2C. Line rates and data throughput have undergone multiple iterations, including 400 kbit/s fast mode, 1 Mbit/s fast-mode plus, 3.4 Mbit/s high-speed mode, and 5 Mbit/s ultra-fast mode.Despite these improvements, the line rates are still insufficient to meet the growing demands for high-speed sensors or complex peripherals. Designers face challenges in achieving interrupts by polling devices or using separate GPIO lines, which undermines the simplicity of the two-wire wiring. Multi-controller setups are complex in arbitration and often not supported by target devices.I3C, developed by the MIPI Alliance, aims to address these limitations while maintaining backward compatibility with traditional I2C devices. The ability to support traditional sensors while enabling new features is why I3C is so important to today’s system designers. I3C has many key advantages over I2C, the most significant being higher throughput. In SDR (Single Data Rate) mode, its clock frequency reaches up to 12.5 MHz, making it ten times faster than I2C’s widely adopted fast mode and more than twice the speed of I2C’s top ultra-fast mode.But it doesn’t stop there, as I3C can also operate in HDR (High Data Rate) mode, pushing performance further to 100 Mbps. The dynamic addressing of I3C allows device addresses to be assigned during bus initialization, unlike I2C’s hard-coded or pin-configurable addresses. This simplifies PCB design and enables more scalable systems. The introduction of in-band interrupts (IBI) eliminates the need for external interrupt lines and allows target devices to issue interrupts in response to controller activity over the same two-wire interface, making I3C an ideal choice for event-driven architectures. Various energy-saving features enable it to achieve higher energy efficiency. Hot-plugging allows devices to dynamically join the bus while it is running, and devices can efficiently enter sleep mode and be awakened. Additionally, unlike I2C, which only supports open-drain operation, the addition of push-pull signaling further reduces power consumption. When evaluating I3C IP cores for projects, keep the following points in mind: compliance with the latest MIPI I3C specifications (v1.1.1 or v1.2); backward compatibility for seamless I2C fallback (which is crucial for mixed environments); configurable roles (including dynamic role switching for auxiliary masters); support for HDR to fully utilize higher data rates when transmitting large data blocks (HDR-DDR, HDR-TSP/TSL, HDR-BT). Transitioning to I3C may be a gradual process, especially in systems using traditional devices. The following indicators suggest it may be time to migrate: you may need higher bandwidth; too many GPIO lines are required for interrupts; your design is power-sensitive; or you may need a future-proof protocol to reduce latency and PCB complexity.ConclusionCompared to the 1980s, today’s embedded systems are faster, more complex, and more power-aware. For decades, I2C has been an indispensable interface in system design and has undergone multiple iterations. I3C was born to meet new challenges, retaining the simplicity of the two-wire interface we are familiar with while providing the performance required by modern systems. If you are building the next ASIC or selecting peripherals for FPGA design, I3C is an excellent choice, not only as a faster bus but also as a great foundation for inter-chip communication.

When evaluating I3C IP cores for projects, keep the following points in mind: compliance with the latest MIPI I3C specifications (v1.1.1 or v1.2); backward compatibility for seamless I2C fallback (which is crucial for mixed environments); configurable roles (including dynamic role switching for auxiliary masters); support for HDR to fully utilize higher data rates when transmitting large data blocks (HDR-DDR, HDR-TSP/TSL, HDR-BT). Transitioning to I3C may be a gradual process, especially in systems using traditional devices. The following indicators suggest it may be time to migrate: you may need higher bandwidth; too many GPIO lines are required for interrupts; your design is power-sensitive; or you may need a future-proof protocol to reduce latency and PCB complexity.ConclusionCompared to the 1980s, today’s embedded systems are faster, more complex, and more power-aware. For decades, I2C has been an indispensable interface in system design and has undergone multiple iterations. I3C was born to meet new challenges, retaining the simplicity of the two-wire interface we are familiar with while providing the performance required by modern systems. If you are building the next ASIC or selecting peripherals for FPGA design, I3C is an excellent choice, not only as a faster bus but also as a great foundation for inter-chip communication.