FPGA has become a strategic technology, regarded as the “poor man’s ASIC”, capable of providing customized ICs for a limited number of applications. At the same time, it has gained strategic importance in the following two large and high-growth applications:

-

Cloud Data Centers: Networking, storage, and security;

-

Communication Systems: Base stations and 5G, etc.

In fact, the strategic significance of FPGAs for data centers has prompted Intel’s acquisition of Altera (completed in 2015), and more recently, AMD’s acquisition of Xilinx. This is because, in many situations, workloads are being shifted from processors to FPGAs.

Data centers that heavily utilize FPGAs can offer parallel programmability that processors cannot achieve (one customer referred to it as “programmability at hardware speed”). These FPGAs are applied in conjunction with ICs that have specific functions, such as network interface chips (NICs) and network switch chips.

Each data center has different workloads, making it impractical to meet all needs with standardized products. Each data center has different scales and capital to optimize based on demand. Communication systems have long used FPGAs to handle hundreds of national frequency bands and communication protocols; in the current 5G environment, FPGAs are used to manage complexity and continuously evolving standards such as O-RAN.

Despite the programmability of FPGAs being quite valuable, the power and size of such components tell another story—today’s data centers and communication vendors want to integrate FPGAs into SoCs to reduce size and power consumption.

FPGA Integration Has Begun

Over the past decade, manufacturers including Achronix, Flex Logix, and Menta have developed the capability to provide embedded FPGA (eFPGA) products. eFPGAs can now be produced using 180nm to 7nm process nodes, with capacities ranging from 1K lookup tables (LUTs) to 100K LUTs, and are soon to reach 1M LUTs, along with DSP and Block-RAM options.

Here are some significant events in the adoption of eFPGAs across the industry:

-

The first customer to successfully use eFPGA was Sandia National Labs in the USA, achieving this at their 180nm fab in New Mexico. Since then, they have manufactured numerous ASICs using eFPGA.

-

Next, Boeing, the US Air Force Research Laboratory (AFRL), Microsoft, BAE, and many other government agencies and contractors have begun to intensively use eFPGA in defense systems manufactured in the USA. Therefore, eFPGA has now become a mature technology for the US Department of Defense and the Department of Energy.

-

Chinese manufacturer Datang Telecom’s chip design subsidiary Morning Core announced it will use eFPGA in vehicle-to-vehicle communication FinFET ASICs.

-

Dialog (acquired by Renesas) launched the ForgeFPGA series eFPGA products in November 2021, starting at 1K LUT with a unit price below 50 cents and power consumption of only a few milliwatts.

-

Flex Logix adopted eFPGA on its 16nm AI inference chip, achieving performance exceeding 500MHz, which can be enhanced to 667MHz or even 800MHz over time with software improvements.

-

Socionext is collaborating with a major systems company to develop a 7nm SoC utilizing eFPGA and 100K LUT programmable logic circuits, ensuring the chip can perform over 500 MHz even in the worst-case scenario. This is a 5G application and is the first mass-produced communication chip integrating a large number of LUTs.

In addition to the above events, many more customers utilizing eFPGA have not yet been disclosed. As awareness of this technology increases, the pace of customer adoption of eFPGA is accelerating; leading companies utilizing eFPGA are also gaining significant competitive advantages in their respective market sectors.

Integrating FPGA Enables More Powerful Software Control

FPGAs have significant advantages, but they are not easy to program; and there are fewer qualified FPGA programmers compared to processor programmers. Why is FPGA programming so difficult? The main reasons are as follows:

-

Verilog is a low-level programming language that resembles assembly more than C++.

-

For traditional programmers, parallel programming is hard to understand and learn.

-

FPGAs are programmed as a huge block of code, while processors consist of subroutines, main programs, linkers, loaders, paging, etc.; programmers take these for granted, but they do not apply to FPGAs.

-

FPGAs can be programmed in seconds and exist permanently in hardware, but typically the entire FPGA must be reprogrammed; some can be partially programmed, but execution is slow, and all operations pause as a result. In processor code, paging continues to swap in/out of cache while the main execution continues.

eFPGA provides an opportunity to rethink this programming strategy—using rare Verilog encoders and allowing C++ encoders to control FPGAs through software. Here’s a basic concept of one approach.

First, containerize/module the program code into subroutines.

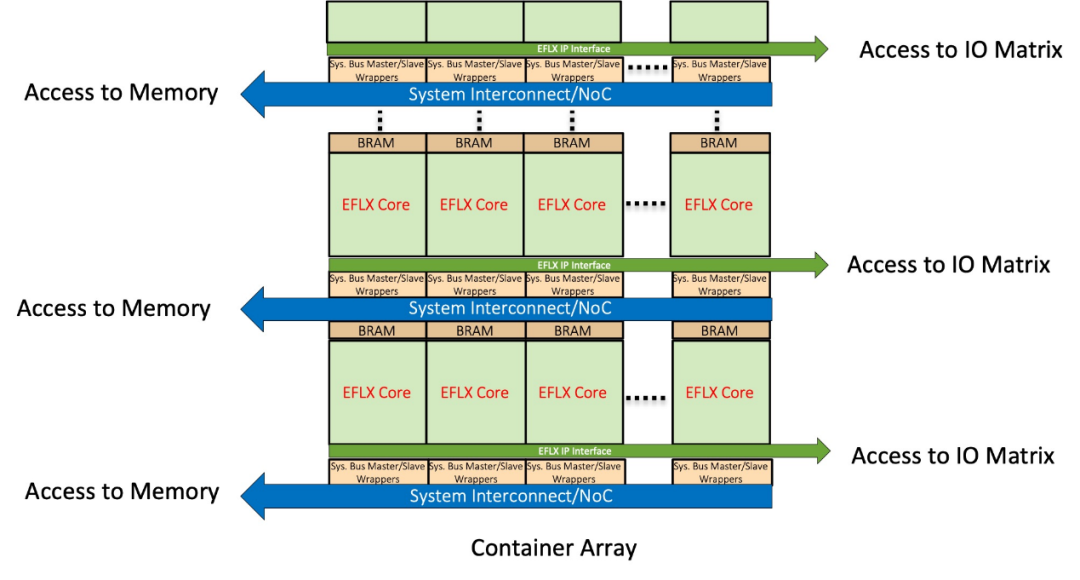

Divide an FPGA into smaller modules or containers, allowing them to directly access DRAM memory and the processor. eFPGA is constructed in a modular way, allowing rows and tiles to be “snapped together” using block RAM (BRAM) as needed. This makes it easy to add a system interconnect/network-on-chip (NoC)/AXI bus, enabling each FPGA module/container to access memory/processor.

Now, write the FPGA program code to operate like a subroutine contained within a container, providing input data or pointing to data in system memory; then let the FPGA execute it, passing the results as output data or pointing to data in system memory. Use rare Verilog encoders to write those “subroutines” that require intensive computation, and then let C++ encoders write the program code on the processor, calling those subroutines when needed.

Array of containerized FPGA program codes.

Second, make the size of the containers/modules variable.

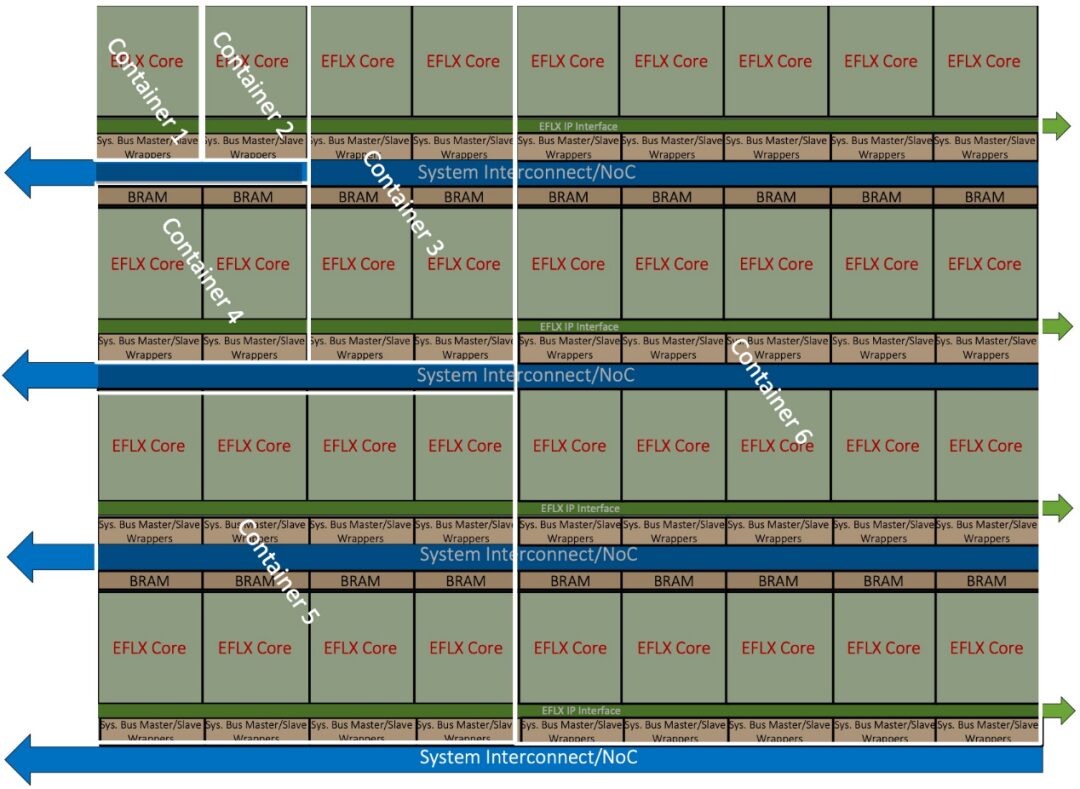

Cutting the FPGA into smaller modules or containers allows them to directly access DRAM memory and the processor. Some algorithms are simpler and use fewer LUTs, while others will use more LUTs. For example, using Flex Logix’s flexible interconnect structure allows containers to become rectangular of any size, up to the size of the entire array.

The size of the containers can be changed.

Third, containers can be paged in microseconds.

FPGAs can always perform programmable actions from flash memory in seconds—very slow, and generally not done often: only when booting or needing an upgrade, like upgrading an iPhone.

However, eFPGA has now been able to be reprogrammed at millions of times per second on leading AI inference processors; this is necessary because inference accelerators require tens of billions of operations to process a neural network layer, needing to be reconfigured in less than 10 microseconds, and then resume operations.

This microsecond-level reconfiguration can be applied to the containers and modules in the above array. When one container is reconfigured, the remaining containers continue to operate at full speed. This allows eFPGA to page like a processor.

Take Control of Your FPGA

We have witnessed the industry evolve from simple arithmetic logic units (ALUs) to processors, microprocessors, parallel processors, and now to SoCs (including processor cores and accelerators). Today, we have reconfigurable SoCs that can better harness the advantages of having a large number of cores in a system.

eFPGA will enable customers in data centers and communications to continue benefiting from the parallel programmability of FPGAs while reducing power consumption, minimizing size, and enabling software control of FPGAs to enhance productivity and shorten time to market. For all these reasons, eFPGA represents a new paradigm shift in computing architecture, increasing computing density per rack through integration while allowing more C++ programmers to enjoy the benefits of eFPGA.

For all these reasons, the integration of eFPGA will accelerate and allow more LUTs to be integrated into SoCs, surpassing the number of LUTs sold in FPGAs over the last decade.

Author: Geoff Tate, CEO of Flex Logix

Original article from EET Electronics Engineering Magazine