Skip to content

1. What are Setup and Hold Times?

Answer: Setup time refers to the time during which the data signal must remain stable before the clock edge, while hold time refers to the time during which the data signal must remain stable after the clock edge.

If the setup and hold times are not satisfied, the DFF will not get the correct sampling data, and the D flip-flop will enter a metastable state, which is an uncertain state.

If the data signal exceeds the setup and hold times before and after the clock edge, the excess time is referred to as setup time margin and hold time margin, respectively.

2. What are the phenomena of race and hazard? How to judge and eliminate them?

Answer: In combinational logic, due to different delays in the input signal paths of gates, the inconsistent arrival times at the gate are called race conditions. Glitches are called hazards. If there are opposite signals in the Boolean expression, race and hazard phenomena may occur. Solutions include adding terms to eliminate the Boolean expression or adding capacitors externally to the chip.

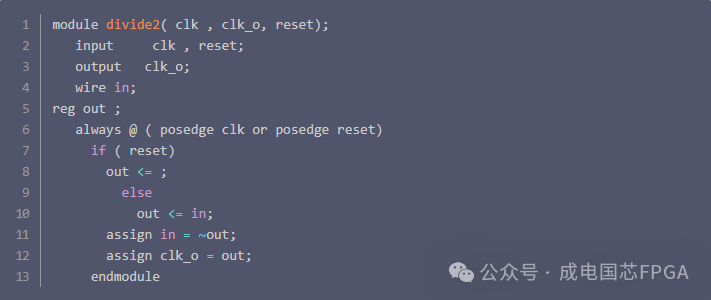

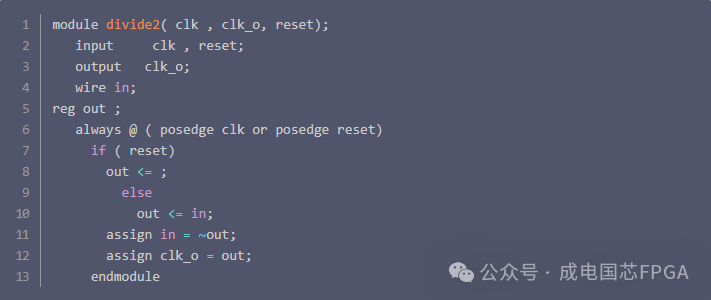

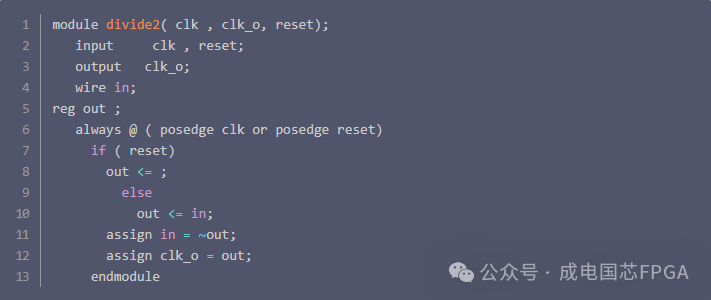

3. How to implement a 2x frequency divider using D flip-flops?

4. What is