16861A 34-Channel Portable Logic Analyzer

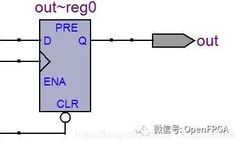

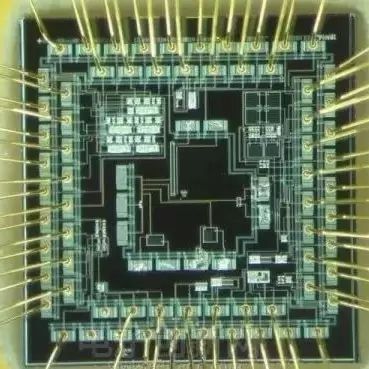

Click the blue text | Follow us 16861A 34-Channel Portable Logic Analyzer Overview The 16861A portable logic analyzer offers faster deep memory timing capture capabilities, helping you complete digital debugging more quickly. Main Features ◆ ◆ Logic Analyzer Configuration 34 channels, 350 MHz state, 12.5 GHz timing scaling, 2.5 GHz timing, 2 Mb deep memory … Read more