This article mainly introduces the terms related to JTAG that are easily confused:

JTAG

IJTAG

IJTAG (Internal Joint Test Action Group): Refers to the IEEE 1687 protocol. With the development of integrated circuits, more and more IPs are involved in circuit design, requiring a protocol to flexibly access different modules within chips and solve the delivery of IP testing solutions. IEEE 1149.1 needed to be expanded and developed, leading to the emergence of IEEE 1687. IEEE 1687 defines the Instrument Connectivity Language (ICL) to describe component connection relationships; defines the Procedural Description Language (PDL) to describe operations on components; and provides SIB components, achieving flexible access to different modules while being compatible with IEEE 1149.1.

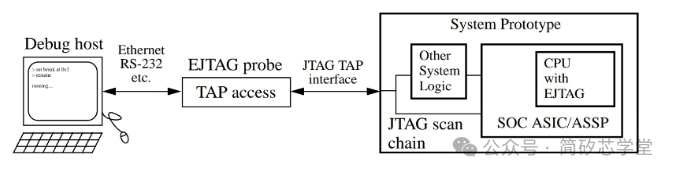

EJTAG

EJTAG (Enhanced Joint Test Action Group): A specification developed by MIPS based on the basic structure and functionality of the IEEE 1149.1 protocol, it is a hardware/software subsystem that implements a set of hardware-based debugging features internally within the processor to support on-chip debugging. It uses the IEEE 1149.1 JTAG test access port (TAP) to input or output test data from the processor core. All MIPS microprocessors or SoC chip components containing MIPS cores support EJTAG debugging.

Figure1 Setup of Debug System with EJTAG

Figure1 Setup of Debug System with EJTAG

XJTAG

XJTAG products are a boundary scan software and hardware suite used for boundary scan work, an innovative boundary scan software and hardware suite that can quickly test, debug, and program complex embedded electronic devices.

XJTAG products use the JTAG test access protocol (built into FPGA, CPLD, and most CPU devices), which can test interconnections on printed circuit boards, designed to help engineers quickly and easily complete PCB debugging and testing, enabling customers to focus on developing better products faster and manufacturing them in a more cost-effective manner. It is a boundary scan solution that provides a universal platform for design and development engineers, test engineers, contract manufacturers, and field test engineers, capable of testing not only JTAG-supported devices but also non-JTAG devices.

END

NEWS

Previous Highlights

HAPPY NEW YEAR

DFT Terminology Simplification (Fifteen) – Diagnosis

DFT Terminology Simplification (Fourteen) – Test Coverage

DFT Terminology Simplification (Thirteen) – OCC/ATPG

DFT Terminology Simplification (Twelve) – EDT

DFT Terminology Simplification (Eleven) – DRC

DFT Terminology Simplification (Ten) – Scan Insertion

DFT Terminology Simplification (Nine) – SCAN

DFT Terminology Simplification (Eight) – IEEE1838

DFT Terminology Simplification (Seven) – IEEE1687

DFT Terminology Simplification (Six) – IEEE1500

DFT Terminology Simplification (Five) – Boundary Scan Part

DFT Terminology Simplification (Four) – Boundary Scan Part

DFT Terminology Simplification (Three) – Fault Model

Recommended to Bookmark! DFT Terminology Simplification (Two)

Recommended to Bookmark! DFT Terminology Simplification!