“When testing the Integral Non-Linearity (INL) and Differential Non-Linearity (DNL) of multi-stage DACs, it is usually unnecessary to perform a full test on all codes. Instead, validation can be achieved by carefully selecting a subset of key codes.”

For example: a 16-bit 3-stage DAC, which internally contains 3 sub-DACs (7-bit, 5-bit, 4-bit), requires scanning all codes, which involves traversing 65536 codes (2^16). However, by scanning the internal sub-DACs, only 176 codes need to be traversed (2^7 + 2^5 + 2^4), as detailed in the code example at the end..

The effectiveness of this method is based on the structural characteristics of multi-stage DACs:

Segmented Testing Principle

-

The testing of multi-stage DACs is essentially an independent analysis and combined verification of multiple small DACs (main DAC + sub-DACs)

-

The INL/DNL of the main DAC (MSB segment) can be assessed by testing the transition points of all its codes.

-

The sub-DAC (LSB segment) only needs to verify its full-scale and key transition points.

-

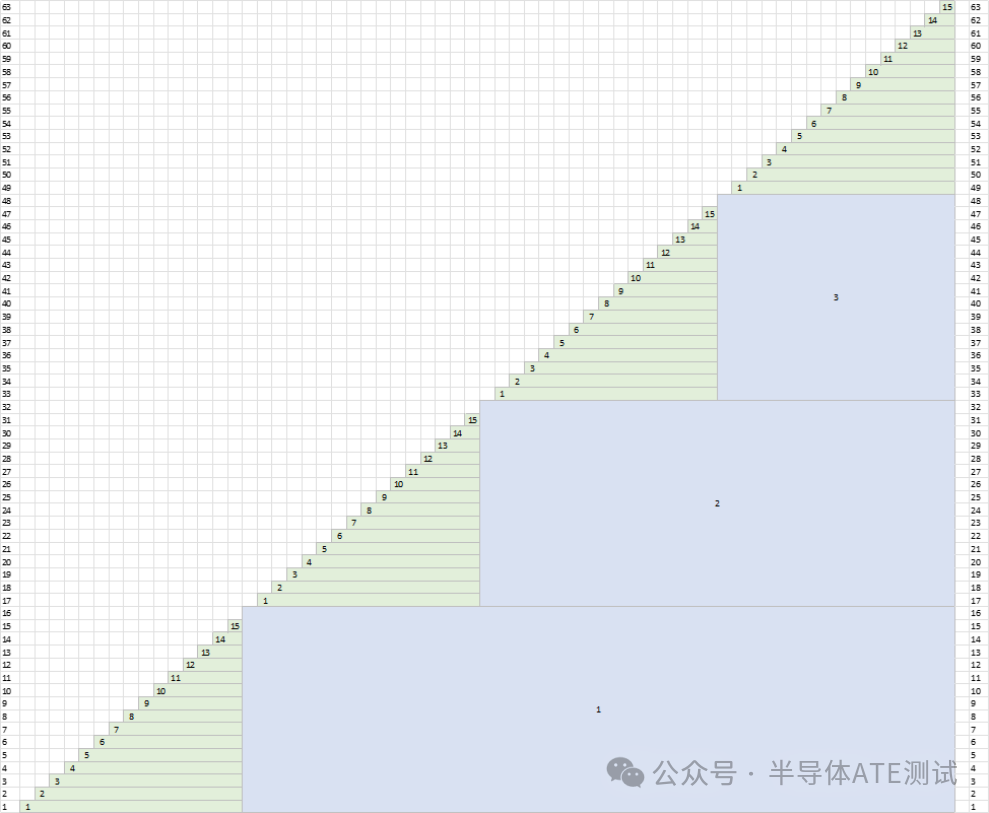

Inter-stage coupling errors can be captured through specific boundary code tests. As shown in the figure below, taking a 6-bit 2-stage DAC as an example: it includes a 2-bit main DAC (blue part) and a 4-bit sub-DAC (green part).

-

The difference (Delta) between any two points on the ramp signal of the sub-DAC (green part) should remain consistent, regardless of how the bits of the main DAC (blue part) are added to the sub-DAC. Therefore, measuring any single segment ramp signal of the sub-DAC is sufficient to fully characterize its properties. Similarly, disabling the sub-DAC and measuring the ramp signal of the main DAC allows for the analysis of the main DAC’s characteristics. The final output of the DAC can be calculated as main DAC characteristics + sub-DAC characteristics..

Additional Notes

-

Delta Consistency:

-

The linearity of the sub-DAC is independent of the code value of the main DAC, which is the core design assumption of segmented DACs.

-

For example: when the main DAC code value switches from

<span><span>00</span></span>to<span><span>01</span></span>, the step (LSB) of the 4-bit ramp of the sub-DAC should remain constant.

Testing Efficiency Optimization:

-

By separating the tests for the main and sub-DACs, traditional full code scanning (e.g., a 6-bit DAC requires testing 64 points) can be simplified to segmented testing (4 points for the main DAC + 16 points for the sub-DAC), significantly reducing testing time.

Error Accumulation Model:

-

If the INL error of the main DAC is

<span><span>ΔM</span></span>and the INL error of the sub-DAC is<span><span>ΔS</span></span>, then the overall DAC output error is<span><span>ΔM + (ΔS / 2^k)</span></span>(<span><span>k</span></span><code><span><span> is the number of bits of the main DAC). This relationship needs to be verified during calibration.</span></span>

2-Stage DAC Testing Example

For a 2-stage DAC composed of a main DAC and a sub-DAC, the testing steps are as follows:

-

Segmented Testing Strategy

✅ Fix the main DAC code value and test all positions of the sub-DAC

-

Keep the main DAC at a fixed code value (e.g.,

<span><span>00</span></span>), scan all possible code values of the sub-DAC (e.g., 4-bit sub-DAC tests 16 points), and record the output. -

Verify the linearity (DNL/INL) of the sub-DAC to ensure its steps (Delta) are uniform.

✅ Fix the sub-DAC to 0 and test all positions of the main DAC

-

Set the sub-DAC to zero (

<span><span>0000</span></span>), scan all code values of the main DAC (e.g., 2-bit main DAC tests 4 points), and record the output. -

Verify whether the steps of the main DAC meet the monotonicity requirements.

-

Monotonicity Guarantee Conditions

If the following condition is met, it can ensure the overall monotonicity of the DAC (the output strictly increases with the code value):

MaxSecDAC (maximum step of the sub-DAC) < MinPrimDAC (minimum step of the main DAC)-

Parameter Calculations:

-

MaxSecDAC =

<span><span>sub-DAC full-scale output - sub-DAC zero output</span></span>(total span of the sub-DAC) -

MinPrimDAC = minimum step between adjacent code values of the main DAC (

<span><span>Min(ΔPrimary)</span></span>) -

MaxPrimDAC = maximum step between adjacent code values of the main DAC (

<span><span>Max(ΔPrimary)</span></span>)

-

Monotonicity Determination:

-

If

<span><span>MaxSecDAC < MinPrimDAC</span></span>, then the DAC must be monotonic.. -

Otherwise, non-monotonicity (output regression) may occur.

-

Worst DNL (Differential Non-Linearity) Calculation

The worst DNL is determined by the maximum of the following two cases:

✅Deviation between the main DAC step and the sub-DAC span:

DNL_case1 = MaxPrimDAC - MaxSecDAC (difference between the maximum step of the main DAC and the total span of the sub-DAC)✅ Sub-DAC's own step non-uniformity:DNL_case2 = deviation of steps between any adjacent code values of the sub-DACFinal Worst DNL : Worst_DNL = Max(DNL_case1, DNL_case2)

3-Stage DAC Testing Example

For a 3-stage DAC composed of a main DAC, sub-DAC, and tertiary DAC, the testing process is an extension of the 2-stage DAC, requiring layered verification of each stage’s characteristics and ensuring overall monotonicity. The testing steps are as follows:

-

Layered Testing Strategy

✅ Fix the main DAC and sub-DAC, test all positions of the tertiary DAC

-

Set the main DAC and sub-DAC to fixed code values (e.g.,

<span><span>00</span></span>and<span><span>0000</span></span>), scan all code values of the tertiary DAC (e.g., 4-bit tertiary DAC tests 16 points). -

Verify the linearity (DNL/INL) of the tertiary DAC to ensure its steps (Delta) are uniform.

✅ Fix the main DAC, set the tertiary DAC to zero, test all positions of the sub-DAC

-

Fix the main DAC (e.g.,

<span><span>00</span></span>), set the tertiary DAC to zero (<span><span>0000</span></span>), scan all code values of the sub-DAC (e.g., 4-bit sub-DAC tests 16 points). -

Verify whether the steps of the sub-DAC meet the monotonicity requirements.

✅ Set the sub-DAC and tertiary DAC to zero, test all positions of the main DAC

-

Set both the sub-DAC and tertiary DAC to zero (

<span><span>0000</span></span>and<span><span>0000</span></span>), scan all code values of the main DAC (e.g., 2-bit main DAC tests 4 points). -

Verify the stepping characteristics of the main DAC.

-

Monotonicity Guarantee Conditions

✅ Sub-DAC Monotonicity Condition

FullTertDAC (full span of the tertiary DAC) < MinSecDAC (minimum step of the sub-DAC)Parameter Calculations:

-

FullTertDAC =

<span><span>tertiary DAC full-scale output - tertiary DAC zero output</span></span> -

MinSecDAC = minimum step between adjacent code values of the sub-DAC (

<span><span>Min(ΔSecondary)</span></span>) -

MaxSecDAC = maximum step between adjacent code values of the sub-DAC (

<span><span>Max(ΔSecondary)</span></span>)

Determination:

-

If

<span><span>FullTertDAC < MinSecDAC</span></span>, then the sub-DAC segment guarantees monotonicity. -

Worst DNL of the sub-DAC =

<span><span>MaxSecDAC - FullTertDAC</span></span>

✅ Main DAC Monotonicity Condition

FullSecDAC (full span of the sub-DAC) < MinPrimDAC (minimum step of the main DAC)-

Parameter Calculations::

-

FullSecDAC =

<span><span>sub-DAC full-scale output - sub-DAC zero output</span></span> -

MinPrimDAC = minimum step between adjacent code values of the main DAC (

<span><span>Min(ΔPrimary)</span></span>) -

MaxPrimDAC = maximum step between adjacent code values of the main DAC (

<span><span>Max(ΔPrimary)</span></span>)

Determination:

-

If

<span><span>FullSecDAC < MinPrimDAC</span></span>, then the main DAC segment guarantees monotonicity. -

Worst DNL of the main DAC =

<span><span>MaxPrimDAC - FullSecDAC</span></span>

For a 7-bit main DAC + 5-bit sub-DAC + 4-bit tertiary DAC, the 16-bit segmented DAC:

primDACBits = 7;subDACBits = 5;tertDACBits = 4;DACBits = primDACBits + subDACBits + tertDACBits;fullSubDAC = pow(2,subDACBits) - 1; // all SubDAC bits enabled// Measure each tertDAC Position, 16 measurements for 4 bitsstaticPos = pow(2,DACBits - 1); // set the mainDAC + subDAC to static positions (half-scale)for(tertDACPos = 0; tertDACPos < pow(2,tertDACBits); tertDACPos++) { MeasureDAC(staticPos + tertDACPos);}// Measure Each SubDAC Position with 0 tertDAC + static MainDAC; 32 measurements for 5 bitsstaticPos = pow(2,DACBits - 1); // set the mainDAC + subDAC to static positions (half-scale)for(subDACPos = 0; subDACPos < pow(2,subDACBits); subDACPos+=pow(2,tertDACBits)) { MeasureDAC(staticPos + subDACPos);}// Measure Each MainDAC Position with 0 tertDAC + 0 subDAC; 128 measurements for 7 bitsstaticPos = 0; // set the subDAC + tertDAC to 0for(primDACBits = 0; primDACBits < pow(2,DACBits); primDACBits +=pow(2,subDACBits + tertDACBits)) { MeasureDAC(staticPos + primDACBits );}// With positions measured, now just calculate INL/DNLThat’s all for the multi-stage DAC testing (It’s really hot outside!)