Source: Content from Yushi Capital, thank you.

RISC-V is an Instruction Set

RISC-V, generally pronounced as: risk five. V, which is the Roman numeral for 5. This instruction set is the fifth generation of the RISC series instruction sets.

RISC-V is an open-source instruction set architecture based on the principles of “Reduced Instruction Set Computer (RISC)”.

The instruction set: stored within the CPU, guides the CPU in calculations, and helps the CPU operate more efficiently, serving as a collection of program instructions that lie between software and underlying hardware.

Two Major CPU Instruction Sets: CISC and RISC

The CPU (Central Processing Unit), also known as a microprocessor, is akin to the brain of electronic products. In the communication field, almost all important information is controlled by this “brain”; CPU chips and operating systems are the foundational core technologies in the field of internet security.

There are two main instruction sets for CPUs:

Complex Instruction Set Computer (CISC) architecture – x86

Reduced Instruction Set Computer (RISC) architecture – ARM, MIPS, and RISC-V

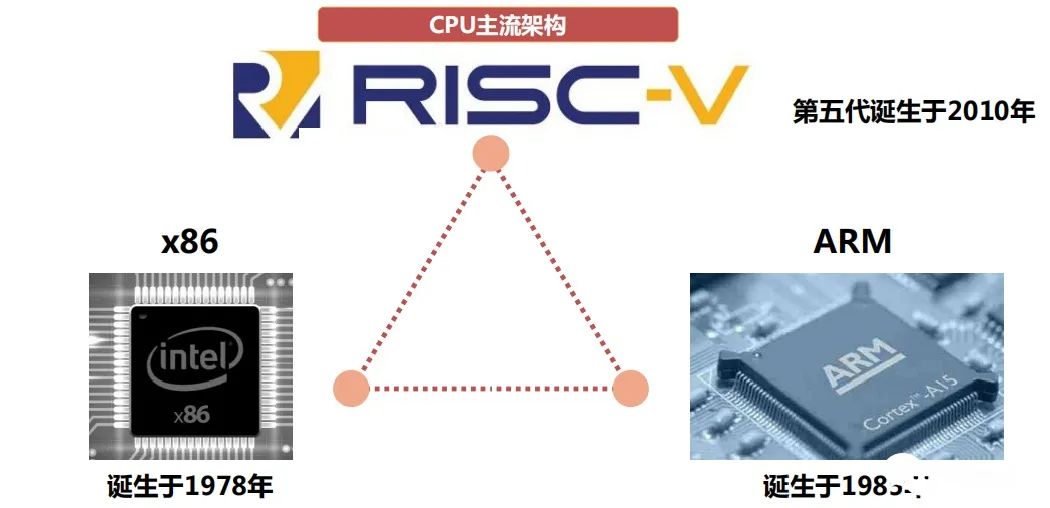

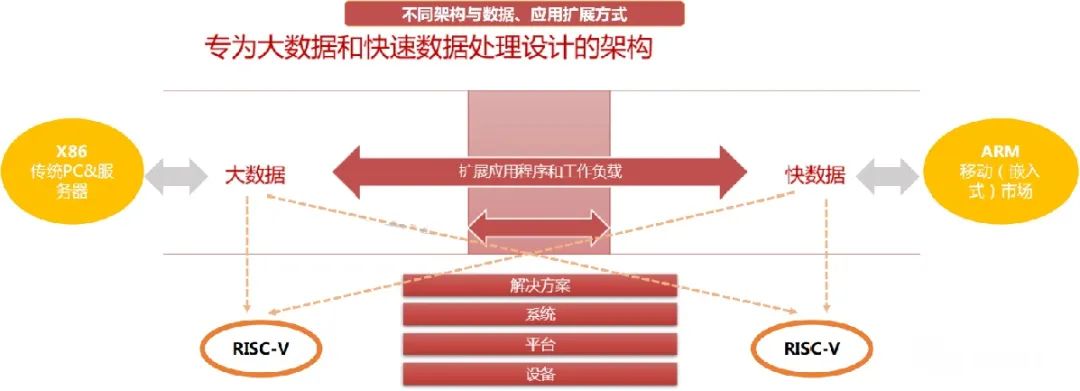

The architecture of CPUs has traditionally been dominated by x86 and ARM, but since the advent of RISC-V in 2010, there has been a subtle trend towards a tripartite balance in CPU architecture.

Mainstream CPU Architectures: x86, ARM, RISC-V

X86: The mainstream in the traditional PC market, adept at handling large data, with IP controlled by Intel and AMD.

ARM: Dominates the mobile (smartphone) market, primarily handling fast data, and is now also used in portable laptops, with most IP held by ARM Holdings.

RISC-V: When there is a need to balance both data transfer speed and volume, the capabilities of these two mainstream architectures are limited. RISC-V has shown strong advantages.

The Development History of RISC-V

In 1981, under the leadership of David Patterson, a research team at the University of California, Berkeley drafted RISC-1, which serves as the foundation for today’s RISC architecture. Subsequently, in 1983, the RISC-II prototype chip was released, followed by RISC-III and RISC-IV in 1984 and 1988, respectively.

The design philosophy of RISC has also led to the emergence of a series of new architectures, such as MIPS, the king of servers IBM PowerPC, and ARM, which now dominates the embedded market.

In 2010, the research team at the University of California, Berkeley designed and launched a free and open instruction set architecture RISC-V based on the BSD protocol license, with its prototype chip successfully taped out in January 2013.

The Design Philosophy of RISC-V: Simplicity Meets CPU Processing Needs

The greatest feature of RISC-V lies in its “simplicity”. Although it belongs to the reduced instruction set architecture like ARM, RISC-V was launched in recent years and does not carry the historical burden of backward compatibility, making the architecture compact and efficient. Compared to x86 and ARM, which often span hundreds to thousands of pages, RISC-V’s specification document is only 145 pages long, and the “privileged architecture document” is merely 91 pages.

Advantages of RISC-V: Modularity and Fewer Instructions

1. Modularity: RISC-V organizes different parts in a modular way and attempts to meet various application scenarios through a unified architecture; this modularity is not present in x86 and ARM architectures.

2. Fewer Instructions: Thanks to its compact architecture and modular characteristics, the number of instructions in the RISC-V architecture is very concise. The basic RISC-V instruction set consists of only over 40 instructions, and with additional modular extension instructions, there are only a few dozen instructions in total.

Advantages of RISC-V: Open Source, Completely Free and Open

RISC-V is fully open source and comes with a complete set of open-source free compilers, development tools, and software development environments (IDE). Its open-source nature allows any user to freely modify and extend it to meet customized requirements, significantly lowering the barriers to modifying the instruction set.

In comparison, ARM requires high IP fees to use similar products and may even require “prepayments” to see the details.

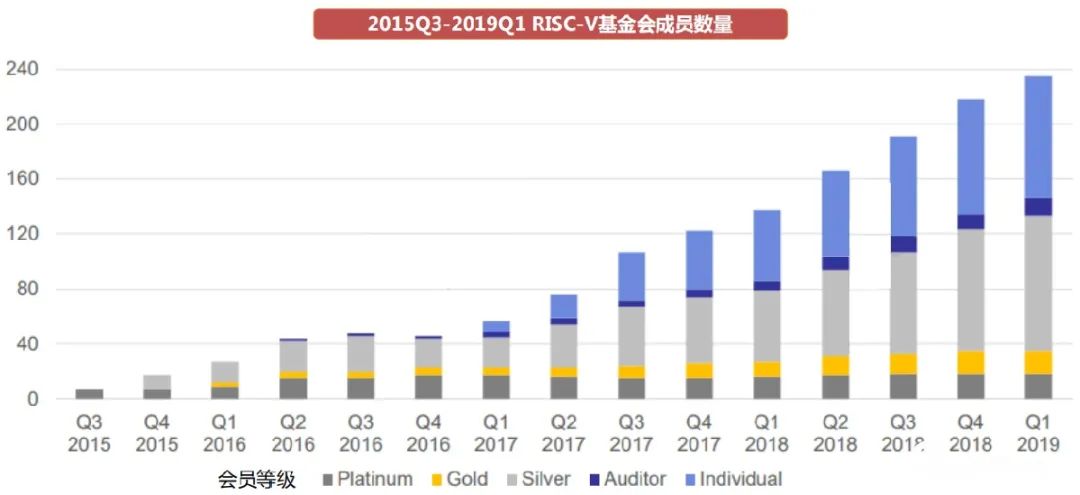

Over 200 Organizations Participating in the RISC Foundation

In 2015, the RISC-V Foundation was officially established, attracting companies such as NVIDIA, NXP, Samsung, and Microsemi. To date, the foundation has attracted over 327 members from 28 countries worldwide. The RISC-V Foundation is responsible for maintaining the RISC-V instruction set standard manuals and architecture documents, and each year it holds various thematic discussions and global events.

The Era of IoT Has Arrived, RISC-V Has Great Potential

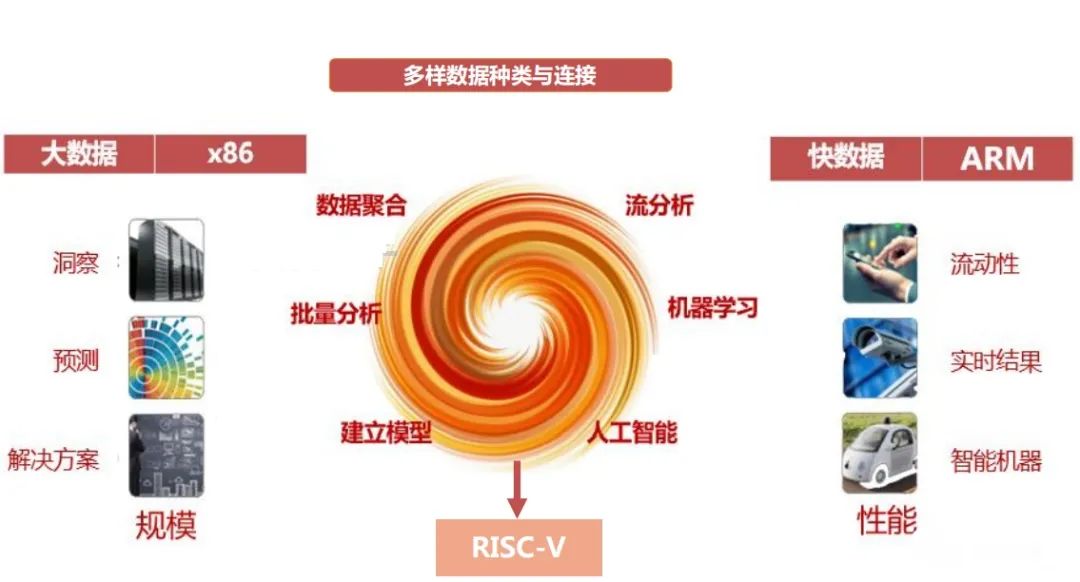

Because x86 is suitable for processing large amounts of data, it dominates the traditional PC and server fields.

In the technological revolution brought about by smartphones, there is a need for fast data processing, and the ARM architecture reigns supreme in the smartphone processor IP domain.

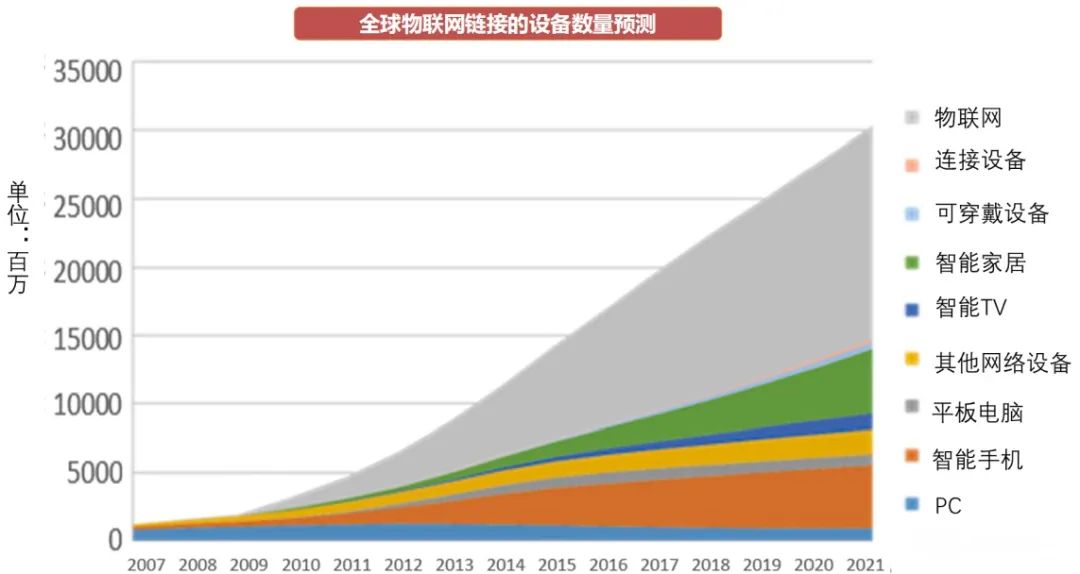

In the history of semiconductors, x86 and ARM have maintained a significant market share as mainstream architectures. With the advent of the IoT era, RISC-V, as an emerging architecture, may achieve absolute advantages in the future IoT field due to its compact structure.

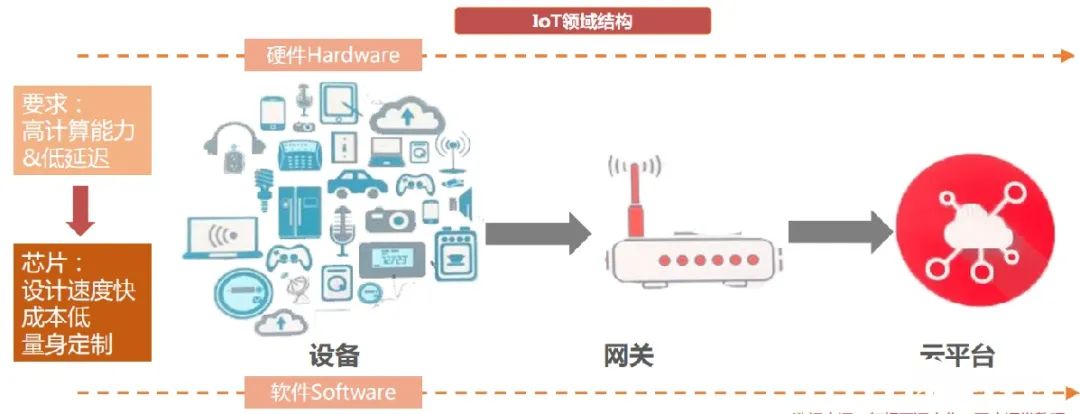

Application of RISC-V: The Fragmented Demand in IoT, Competition Among Many

In the IoT field, AI chips require both high computing power and low latency.

Thus, IoT chip design needs to be fast, cost-effective, and customizable.

Moreover, the embedded market has the characteristic of being small and diverse, with no real barriers formed in various sub-application scenarios; the choice of architecture is varied.

Therefore, this presents an excellent breakthrough opportunity for RISC-V. The open-source nature of RISC-V can reduce costs and allow users to freely modify it, making it customizable. The RISC-V ecosystem and agile design share the same origin. Currently, both domestic and foreign chip companies have invested heavily in researching the applications of RISC-V in the IoT field.

Application of RISC-V: Security Issues in IoT

In the future, the IoT is expected to connect around 30 billion devices, making IoT security a necessity, not a luxury. The open-source characteristic of RISC-V allows a broad audience to inspect its architecture and correct issues before they lead to widespread security incidents. RISC-V can influence our existing network crime epidemic by providing “fix” cores without requiring actual changes to the core.

Application of RISC-V: The Smartphone Market

According to predictions by SiFive CEO Naveed Sherwani, RISC-V will enter the smartphone market in two years, competing with ARM companies like Qualcomm, Apple, Samsung, and MediaTek for the smartphone processor market, and may also threaten low-power notebook processors.

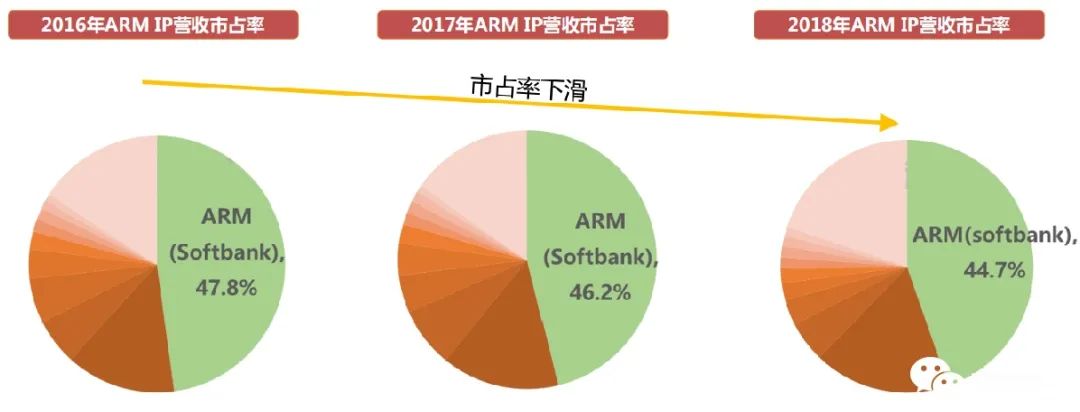

Currently, ARM’s revenue data has slightly declined, with ARM’s design IP market share dropping by 1.6% and 1.5% in 2017 and 2018, respectively. Consequently, ARM has implemented corresponding improvement strategies. In July 2019, Arm launched a new licensing model called “Flexible Access”: for mid-tier chips, future customers will no longer need to pay a “prepayment” to see design details.

Application of RISC-V: The Server Market

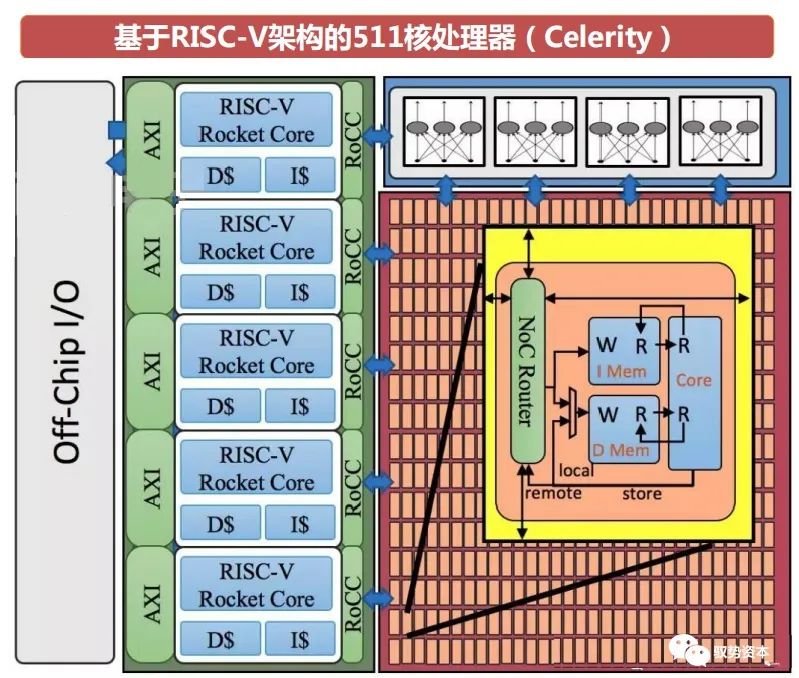

Although the high-performance market for RISC-V is currently vacant, RISC-V is capable of designing high-performance chips. Academia has already developed a 511-core processor (Celerity) based on the RISC-V architecture. However, due to the low entry threshold of RISC-V, the companies entering this field are relatively small and lack sufficient funds for long-term planning and research; no one has ventured into high-performance fields that require long R&D times.

According to SiFive CEO Naveed Sherwani’s predictions, RISC-V instruction processors may enter the server market in five years, raising concerns for x86 processor companies like AMD and Intel.

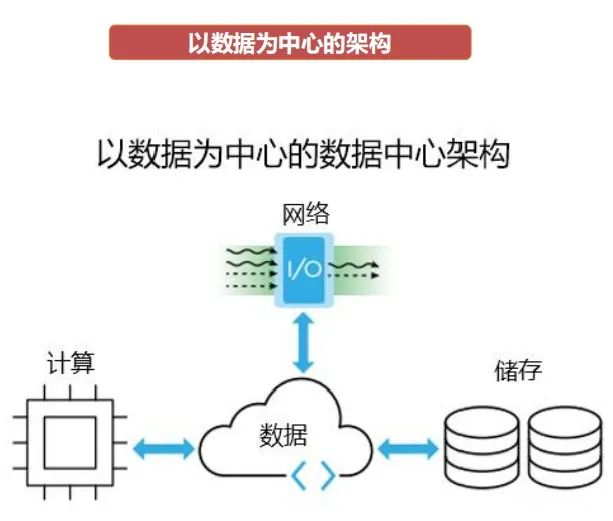

Application of RISC-V: The Storage Market

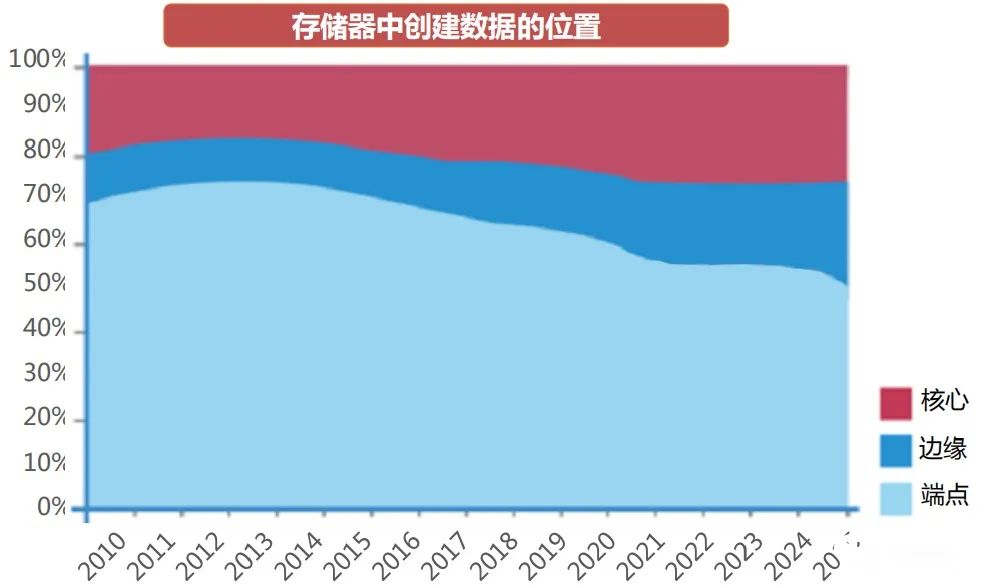

Hard drives do not require as much computational resources as SSDs, but due to new magnetic recording technologies and more complex functions (such as NAND Flash-based caching, health management, QoS), their processing requirements are increasing. This raises the computational power requirements for control chips in storage devices.

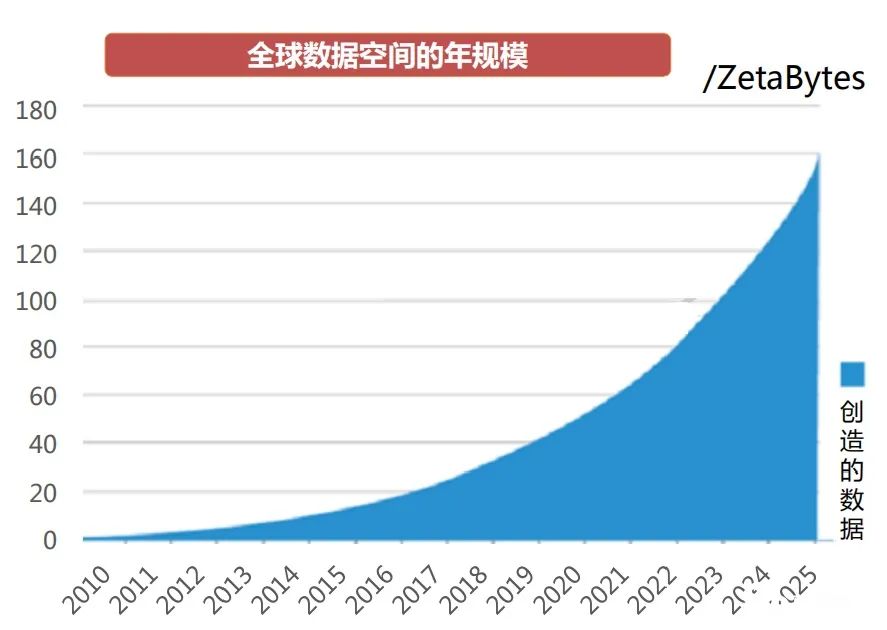

In 2017, according to IDC and Seagate data, 16.1 ZB (ZetaBytes) of data was generated globally in 2016, and by 2025, the global data sphere is expected to grow an order of magnitude to 163 ZB. Moreover, the amount of data requiring real-time processing and low latency is also increasing.

While data can be transmitted nearby to servers for processing, this requires more powerful servers; however, the servers themselves are not efficient at processing fast data, meaning hard drives need not only to store data but also to process it.

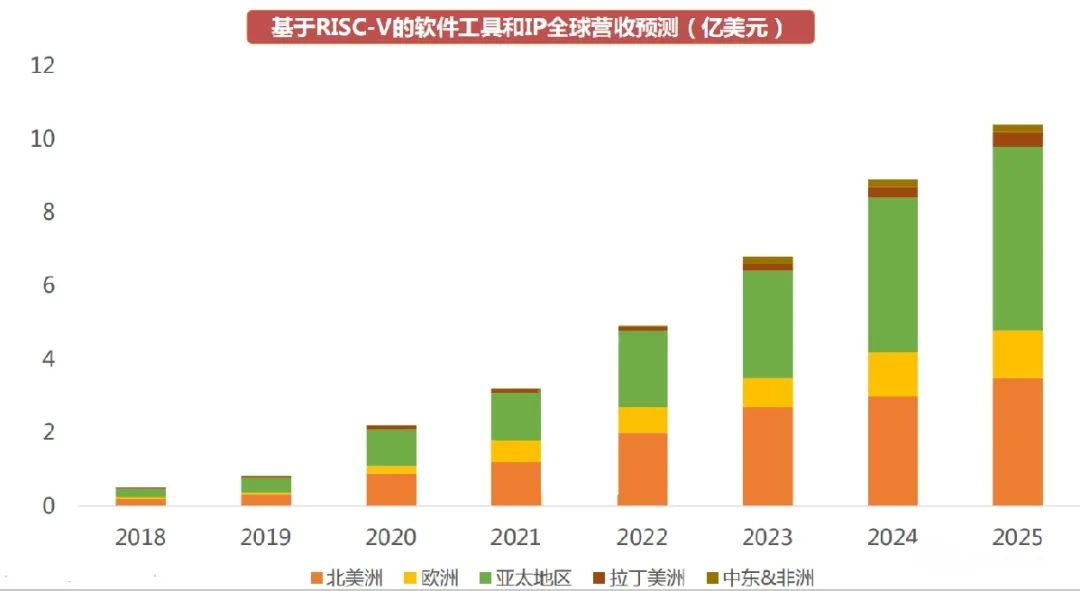

In 2018, Global Revenue from RISC-V Based Software Tools and IP Reached $50 Million, Expected to Increase 20 Times by 2025

Currently, RISC-V is considered most suitable for application in the IoT market. This is because the IoT market is more flexible and fragmented, with customer demands being relatively diverse, and no single architecture currently dominates the market. RISC-V features low power consumption, low cost, flexibility, scalability, and reliability.

Although RICS-V itself is open-source and free, users can sell modifications and uses of the RICS-V architecture. According to Tractica’s predictions, global revenue from RISC-V based IP and software tools will increase to $1.1 billion by 2025, up from $52 million in 2018.

RISC-V Currently Lacks an Ecosystem

The influence of CPU architecture primarily relies on the entire ecosystem it grows within, such as Windows based on x86 and Android based on ARM. What RISC-V currently lacks is an ecosystem, especially given the fragmented nature of IoT, where no unified software stack ecosystem exists.

The RISC-V Foundation does not define this; the building of the ecosystem is left to users to develop. Moreover, ecosystem development is not an overnight process. According to Guo Xiongfei, Deputy Secretary-General of the RISC-V Foundation in the Asia-Pacific region, only when RISC-V MCUs are mass-produced and developers can truly access them will the corresponding software ecosystem explode on a large scale.

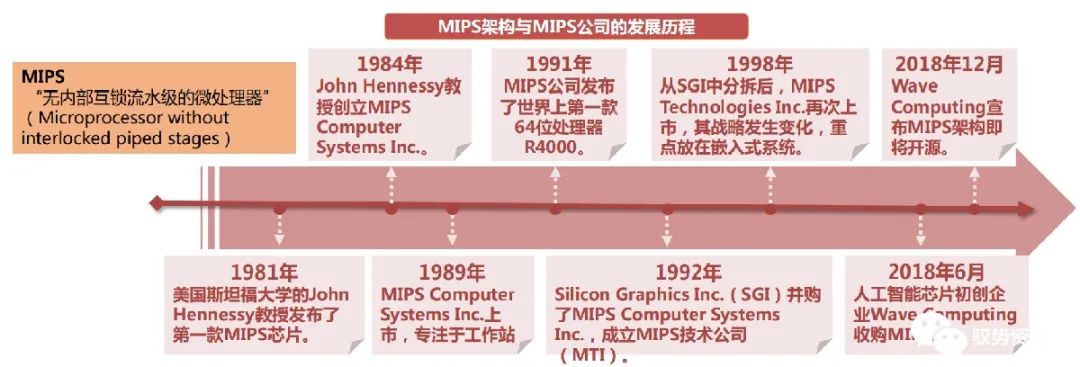

MIPS May Become RISC-V’s Strongest Competitor in the AI Chip Race

ARM, MIPS, and RISC-V all belong to the Reduced Instruction Set Computer (RISC) architecture.

In the smartphone era, while MIPS chose consumer electronics, ARM opted for the smartphone market. Even though ARM and MIPS were born at slightly different times, the later-emerging ARM became the label of the smartphone era.

The architectures of MIPS and RISC-V are also quite similar. Therefore, after MIPS announced its open-source status in December 2018, it may become a strong competitor to RISC-V in the AI era. Additionally, there have been 10 billion chips shipped based on the MIPS instruction set, indicating that MIPS processors have matured in markets such as set-top boxes, voice recorders, and smartwatches. In the future, factors such as policy, ecosystem, and software will be important considerations in the competition between the two instruction sets in the AI era.

RISC-V Represents a Unique Opportunity for Domestic Chip Independence

Currently, all general-purpose x86 architecture processor technologies are held by Intel and AMD, while ARM is also subject to US policy restrictions. Additionally, information security has been a topic of emphasis in recent years. In critical departments such as government, customs, finance, railways, civil aviation, healthcare, and military police, ensuring communication security is particularly vital.

However, the open-source nature of RISC-V allows domestic companies to continue utilizing it. Furthermore, due to its modular design, modules can be directly applied with low entry barriers. In the context of new trends like IoT, RISC-V has significant advantages over other architectures. Domestic companies that lay the groundwork early may become giants in the industry. Since 2018, a wave of discussions about RISC-V has emerged in China’s semiconductor technology circles.

China RISC-V Industry Alliance – Building the RISC-V Industrial Ecosystem

On the morning of September 20, the founding conference of the China RISC-V Industry Consortium (CRVIC) was successfully held at the Shanghai Integrated Circuit Industry Association conference room in Zhangjiang. It attracted participation from numerous units including Xinhaun Holdings, Xilai Technology, Shanghai Saifang Technology, Hangzhou Zhongtian Micro, Beijing Junzheng, Zhaoyi Innovation, and Unisoc, with Xinhaun Holdings serving as the first chairman unit of the alliance.

The establishment of the alliance aims to build an industry exchange platform, promote the widespread application of RISC-V, foster RISC-V talent development, establish university training programs, promote collaborative development among members, and carry out RISC-V global foundation activities to deepen international cooperation and exchange.

Conclusion: RISC-V Has Unique Advantages in Emerging Fields Like IoT