-

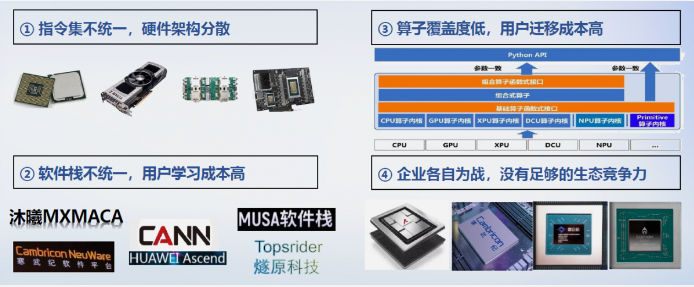

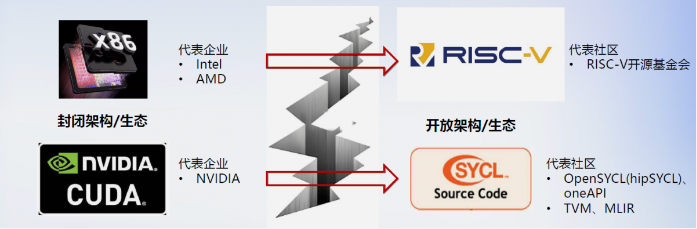

A System (High-speed Rail Model), where the mainstream platform of our informationization is dominated by the X86 and Arm ecosystems. Domestic processors like Haiguang and HiSilicon emphasize “full compatibility”—”Without you, I can’t function”; -

B System (Beidou Model), emphasizing “full autonomy” with Loongson and Shenwei as representatives. Because they do not comply with mainstream market compatibility, their ecosystems are weak—”Without you, I can barely manage”; -

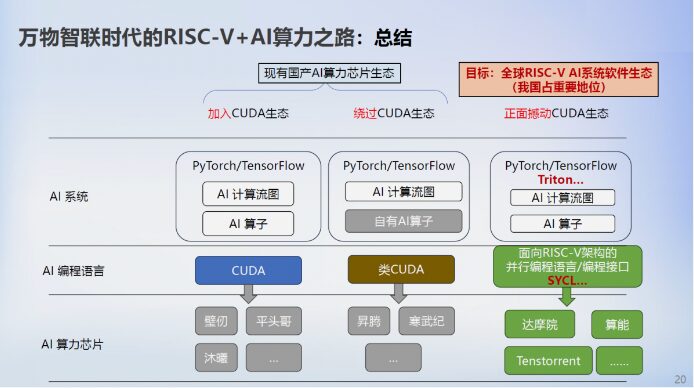

C System (5G Model), taking the “fully open” approach, with the whole world building the ecosystem together, where no one controls anyone, and no one can restrict anyone, such as RISC-V—”You contain me, and I contain you”.

-

Found a DJI drone by the sea! Disassembled and found a pile of chips, made a fortune!

-

Xiaomi reveals the strongest quarterly report ever, is the automotive business loss of 1.8 billion worth it?

-

Disassembled a subwoofer! Let’s see how classic amplifiers are designed

-

What role do these four Schottky diodes play in the circuit?

-

Disassembled Mijia Bluetooth temperature and humidity meter 2, used this to save costs!