In 2010, the Berkeley research team aimed to design a CPU. However, Intel’s licensing for x86 was very strict, ARM’s instruction set licensing was expensive, and MIPS, SPARC, and Open Power also required their respective company licenses. With limited options, the Berkeley research team decided to start from scratch to design a new instruction set. Excitingly, it took only 3 months for four members of the Berkeley research team to complete the development of the RISC-V instruction set. Currently, the Berkeley research team has completed a sequential execution 64-bit processor core (codenamed Rocket) based on the RISC-V instruction set, and has successfully taped out 12 times using 45nm and 28nm processes. The Rocket chip operates at a frequency of 1GHz, demonstrating a performance increase of 10% compared to the ARM Cortex-A5, with an area efficiency improvement of 49%, and its dynamic power consumption per frequency is only 43% of that of the Cortex-A5. In the embedded field, Rocket is already competing with ARM for market share.

The RISC-V instruction set is an open instruction set architecture (ISA) built on the principles of Reduced Instruction Set Computing (RISC). RISC-V is a brand new instruction set developed on the foundation of the continuous evolution and maturation of instruction sets. The RISC-V instruction set is completely open-source, designed to be simple, easily portable to Unix systems, and modular, with a complete toolchain and extensive open-source implementations and tape-out cases, receiving strong support from the community. Although it is not the first open-source instruction set (ISA), it is the first instruction set architecture designed to allow for the selection of suitable instruction sets based on specific scenarios. Servers, household appliance CPUs, industrial control CPUs, and CPUs in sensors can all be designed based on the RISC-V instruction set architecture.

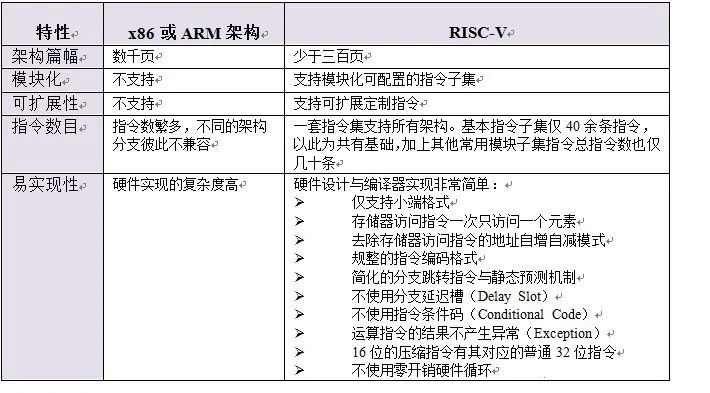

In the field of processors, the mainstream architectures are currently x86 and ARM. However, as commercial architectures, they must retain many outdated definitions to maintain backward compatibility. Over time, this has become extremely cumbersome. The RISC-V architecture, on the other hand, does not require backward compatibility. The current “RISC-V architecture documentation” is divided into the “Instruction Set Document” (riscv-spec-v2.2.pdf) and the “Privileged Architecture Document” (riscv-privileged-v1.10.pdf). The “Instruction Set Document” is 145 pages long, while the “Privileged Architecture Document” is only 91 pages long, making it relatively easy to get started and learn.

The most significant difference of the RISC-V architecture compared to other mature commercial architectures is that it is a modular architecture. Therefore, the RISC-V architecture is not only concise but also organizes its different parts in a modular way, attempting to meet various application needs through a unified architecture. This modularity is not present in x86 and ARM architectures. For example, the ARM architecture is divided into three series: A, R, and M, which correspond to Application (application operating systems), Real-Time (real-time), and Embedded (embedded) fields, respectively, and are not compatible with each other.

The concise architecture and modular philosophy result in a very simple number of instructions for the RISC-V architecture. The basic number of RISC-V instructions is only over 40, and with other modular extension instructions, there are only a few dozen instructions in total.

Image source: “Silicon Farmer Alexander”

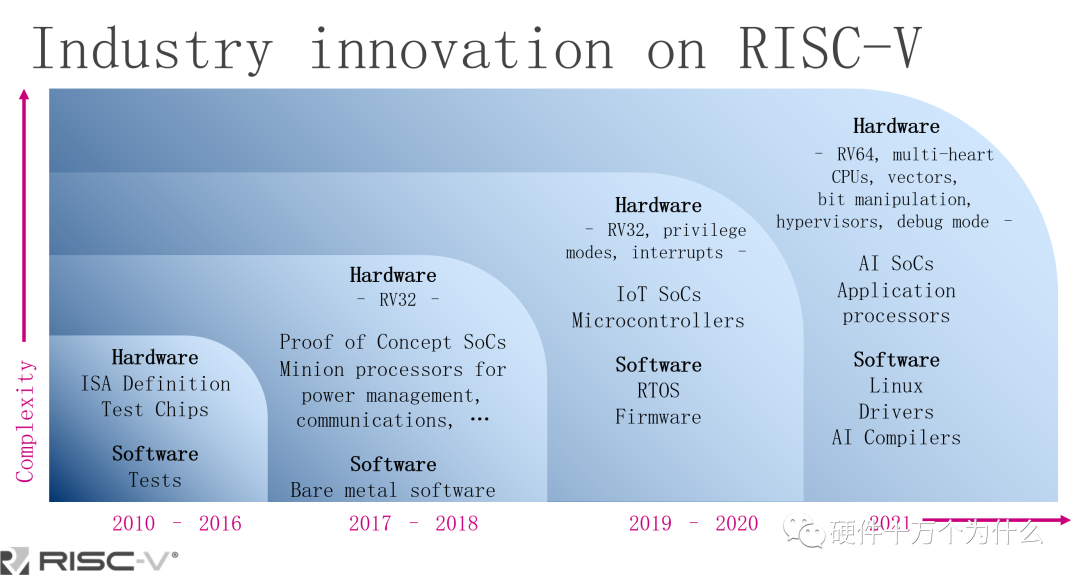

RISC-V is a free and open ISA that has ushered in a new era of processor innovation through collaborative open standards. The RISC-V ISA provides a new level of freedom and scalability in software and hardware architecture, paving the way for design and innovation in computing for the next 50 years.

The Development and Progress of RISC-V

RV64 became a new hotspot in 2021

This year’s RISC-V China Summit saw the hardware team of “Why 100,000 Questions” also attending, particularly participating in the product presentation and communication activities of Allwinner D1.

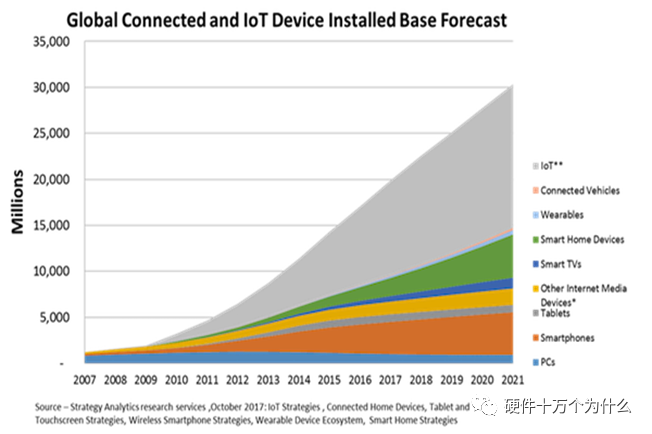

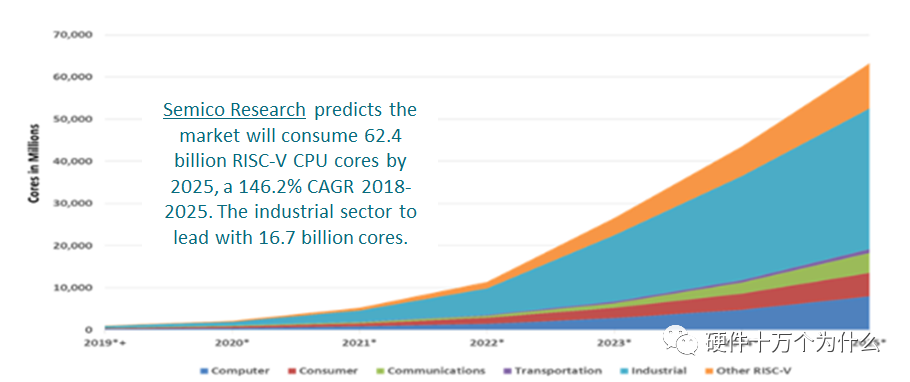

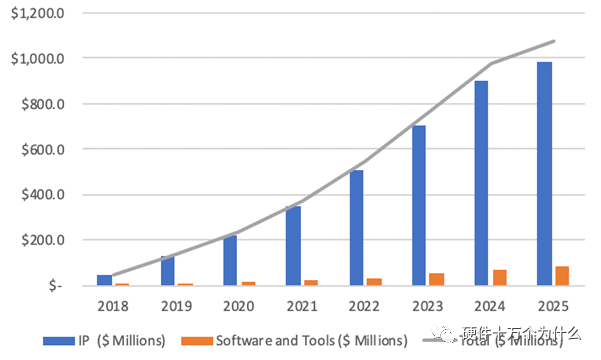

The RISC-V official website predicts RISC-V growth

Joining the RISC-V camp is largely driven by commercial factors

Hundreds of technology companies worldwide have joined the RISC-V camp, largely for commercial reasons. Although many reports attribute ARM’s success to its openness, in reality, ARM is only open in terms of its business model, while being very restrictive in technology.

So far, the number of companies licensed for ARM32 can be counted on one hand. While there are slightly more ARM64 licenses, the licensing fees are exceptionally high. The French startup Greenwave stated that if they were to use the ARM architecture, they would spend $15 million on licensing fees. Moreover, once the license expires, whether to continue licensing and the licensing fees must be renegotiated.

For large companies like Qualcomm, Apple, and Huawei, licensing fees in the hundreds of millions of RMB may not be significant, but for startups, this is an unbearable burden.

In this situation, startups are certainly inclined towards the free RISC-V. Tech giants like IBM, NXP, Western Digital, NVIDIA, Qualcomm, Samsung, Google, and Huawei have also chosen to join RISC-V due to considerations of not putting all their eggs in one basket and dissatisfaction with ARM.

However, this does not guarantee that RISC-V will have a bright future, as most of these tech giants are still observing and are in a “no rabbit, no hawk” mode. Furthermore, RISC-V is completely open-source and allows commercial companies to arbitrarily add instructions, which can easily lead to the fragmentation of RISC-V.

This could make it difficult to form a unified ecosystem, and in the future, it may be the case that RISC-V processors developed by Huawei, Qualcomm, and Google, while all belonging to RISC-V, cannot run the same software. Just as complete openness and strong leadership are contradictory, if this issue cannot be resolved, RISC-V may struggle to grow to a level where it can compete with x86 and ARM.

Main Members