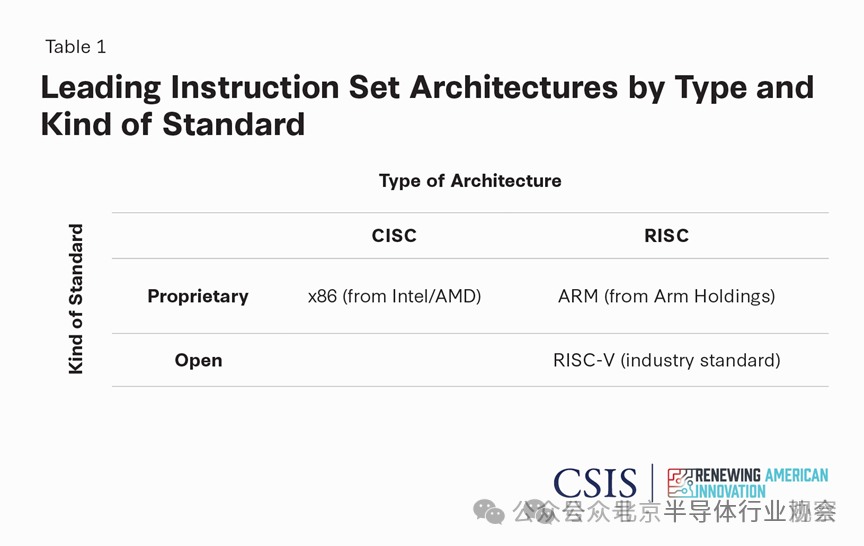

(Source: csis)The RISC-V architecture is an open international standard that specifies the interface between computer software and hardware. It serves as a shared language, setting parameters for communication and interoperability. The open standard provides a pathway for industry participants to collaborate and develop technological solutions, helping to accelerate innovation and limit the abuse of intellectual property (IP).Some policymakers are concerned that open standards may threaten U.S. national security and competitive advantage. However, the openness of the standard itself does not pose a risk. In fact, RISC-V does not contain sensitive intellectual property, and its collaborative development does not require companies to disclose their IP. Companies compete on the technologies developed using the platform, not on the platform itself. RISC-V enhances the competitiveness of U.S. chip design companies by creating a flexible, low-risk, and low-cost collaborative platform. To seize this opportunity, the U.S. should continue to support the application of RISC-V in future chip innovations.RISC-V in the ISA LandscapeCurrently, two leading semiconductor instruction set architectures (ISAs) dominate the market: x86 (from U.S. companies Intel/AMD) and ARM (from U.K. company Arm Holdings, which is owned by Japan’s SoftBank Group). ISAs primarily fall into two categories: Complex Instruction Set Computer (CISC) and Reduced Instruction Set Computer (RISC), which differ in their organization and operational efficiency; x86 is based on CISC principles, while ARM is based on RISC. Most laptops and desktops use the x86 ISA, while ARM holds nearly the entire market share in mobile. Both ARM and Intel/AMD ISAs are proprietary standards, meaning other companies and designers must license ARM IP or purchase and use processors based on Intel/AMD IP. In contrast, the latest entrant in the field is RISC-V (pronounced “risk five”), an open standard ISA based on RISC principles, which chip design teams can access and implement freely across various use cases without licensing restrictions. In other words, RISC-V allows for easy customization through royalty-free licenses and imposes no licensing restrictions on modifications.Global Platform: RISC-V was initially developed in 2010 at the Parallel Computing Laboratory at the University of California, Berkeley, and is now managed by the Swiss non-profit standards organization RISC-V International. This non-profit organization has attracted 4,600 members from 70 countries, including companies, universities, community organizations, and individuals collaborating on the development of the RISC-V ISA and its extensions. The Technical Advisory Board of RISC-V International includes U.S. entities (such as Google and Qualcomm) as well as Chinese organizations (such as Alibaba and Huawei). The 24 primary members of RISC-V International include startups, venture capital firms, and hyperscale companies, with 12 located in mainland China, 9 in the U.S., and one each in Taiwan, Brazil, and Spain. The board and overall membership are distributed across the U.S., China, and Europe, with the U.S. slightly leading in numbers.Flexibility and Accessibility: The flexibility and accessibility of RISC-V make it an extremely attractive and rapidly growing ISA. Early use cases have primarily focused on the embedded systems market, with potential applications in high-performance computing (HPC), artificial intelligence (AI), consumer electronics, and wearable devices. Currently, the number of RISC-V-based chips has exceeded 2 billion, and it is expected to grow to 20 billion by 2031. The membership of RISC-V International has increased from 236 in 2019 to over 4,600 by 2025, as the organization is committed to leveraging this support. At the end of 2019, escalating geopolitical tensions prompted RISC-V International’s management to move from Delaware to Switzerland, citing its mission to ensure that universities, governments, and businesses outside the U.S. can access and develop its technology. Since then, the non-profit organization has been building collaborative tools and opportunities within the ecosystem and has established 68 new specifications and over 80 working groups.Low-Cost, High-Control Platform: Many companies currently purchasing x86 or ARM ISA licenses are participating in the development of RISC-V to gain another semiconductor architecture option without paying high licensing fees. This allows engineers to build their implementations on top of the ISA, giving them better control over their technology and fully leveraging the software compatibility of the RISC-V ecosystem. For example, just five years after the launch of the RISC-V open standard ISA, Nvidia began transitioning from its proprietary microcontrollers to RISC-V-based cores in 2015. Other industry giants like Google, Qualcomm, and Samsung have taken similar steps. The customizable, low-cost ISA option is also attractive to small businesses.Secure IP Environment: It is important to emphasize again that RISC-V does not contain sensitive IP, and its collaborative development does not require companies to disclose such IP. The standardization of RISC-V does not require U.S. companies to share confidential information with others. Companies’ sensitive IP is only used for their RISC-V implementations and is not shared through the RISC-V platform itself, and companies can license their RISC-V implementations. For instance, startups like SiFive and Tenstorrent use the RISC-V ISA and then license their implementations as IP. Additionally, some believe that open-source ISA designs are more secure than closed designs because they allow members of the tech community to collaboratively identify vulnerabilities.The standardization of RISC-V does not require U.S. companies to share confidential information with others. Companies’ sensitive IP is only used for their RISC-V implementations and is not shared through the RISC-V platform itself, and companies can license their RISC-V implementations.The Business Case for RISC-VRapid Industry Adoption: According to BCC Publishing, the market revenue for RISC-V technology is expected to grow at a compound annual growth rate of 33.1% from 2022 to 2027. The U.S. Defense Advanced Research Projects Agency (DARPA) supported the development of RISC-V multicore processors in 2018. By 2025, many U.S. companies are rapidly investing in RISC-V-based software implementations, from microcontrollers in Nvidia’s GPUs to Samsung’s 5G mmWave RF and Seagate’s HDD controllers. In fact, in May 2023, industry leaders and startups collaborated to launch the RISC-V Software Ecosystem (RISE) project, aimed at accelerating the integration of RISC-V software into consumer electronics, data centers, and automotive products. RISE’s 13 senior members and 10 regular members include Google, Intel, Nvidia, Qualcomm, Red Hat, Rivos, SiFive, Ventana, Samsung, MediaTek, ByteDance, and Tenstorrent.Major industry players have also publicly described the increasingly important role of the RISC-V architecture in AI applications and scaling. In 2018, Google co-founded OpenTitan, aimed at developing an open-source, root-of-trust chip, which has received support from community members as well as industry and academic partners. Qualcomm has used RISC-V cores in some of its Snapdragon processors, with over 650 million such cores shipped. Nvidia revealed in October 2024 that its custom CUDA cores will be based on the RISC-V ISA standard. To date, the company has developed at least three RISC-V microcontroller cores, with expected shipments reaching 1 billion by October 2024.Greater Technical Flexibility: Why are so many companies investing in RISC-V? The answer boils down to flexibility and cost, primarily reflected in supply chain and customizability aspects. Licensing requirements are expensive and fraught with restrictions, not to mention the legal complexities involved. Additionally, RISC-V is currently more technically flexible than earlier ISAs. For example, x86 has undergone long iterations, continually adding extensions and complexity, making it difficult to apply to new applications. RISC-V-based cores do not carry the legacy issues of previous generations and can be more easily customized for performance advantages or higher compute density. As a spokesperson from Ventana Micro explained, “Adding an instruction in RISC-V is a relatively simple process; you just propose the instruction definition, provide the justification needed for the instruction, and have it reviewed by the RISC-V International Technical Advisory Board.”While the recent developments of RISC-V have brought many advantages, its emerging characteristics also mean it does not have the same level of technical and customer support networks as proprietary ISAs. ARM’s proprietary technology comes with support and liability guarantees, while RISC-V International is currently working to build that ecosystem. As a spokesperson from Ventana Micro explained, “Our goal has always been to drive all new instructions/extensions through RISC-V International to prevent industry fragmentation. Even so, if you do need to get something done, you can always push it through quickly and incubate accelerated ideas on a common basis. This is precisely why RISC-V is attracting so many AI applications.”Increasing Adoption of RISC-VRISC-V is not only a competitor to x86 and ARM but also represents a groundbreaking alternative for a wide range of current and potential applications in chip design.Current Applications: Currently, RISC-V is primarily applied in embedded technology, with broad market prospects in wearable devices, global automotive, and HPC/AI industries. The fabless company SiFive is an early supporter of RISC-V high-performance chips, with its chips used in Google data centers and NASA’s high-performance space computers. RISC-V is also used to build flexible chips that power wearable medical electronics, smart packaging tags, soft robotics, and other low-cost products.Future Applications: While RISC-V may not compete with x86 and ARM in mainstream consumer electronics applications for at least a decade, leading companies are already using RISC-V to develop future capabilities. Alibaba is developing RISC-V chips for edge computing, and Hong Kong-based DeepComputing has released the world’s first RISC-V laptop, although its performance currently lags behind laptops using proprietary ISAs. In 2024, engineers from Intel’s Advanced Architecture Development Division founded AheadComputing Inc., a startup focused on developing RISC-V core IP.Infrastructure Needs: Crucially, for RISC-V to become a mainstay in mainstream devices, a robust ecosystem of tools, support systems, and resources must be built to attract chip manufacturers and producers. RISC-V International approved the RVA23 specification in October 2024, marking an important milestone; this specification is a set of standardized ISA extensions compatible with RISC-V, although much work remains to support its development ecosystem.RISC-V as a Strategic Opportunity for U.S. Standard Innovation LeadershipGiven the rapid proliferation of the RISC-V platform and its advantages in enhancing interoperability and collaboration, what are the policy options for the U.S.? Recent analyses have highlighted considerations for U.S. policymakers regarding RISC-V policy:Need for Better Understanding of RISC-V: A 2024 review noted that policymakers do not sufficiently understand RISC-V—especially that chip competition occurs at the implementation level, not the standard level. This means that each company implements the ISA in unique ways and independently adds its proprietary innovations. In short, RISC-V does not involve the transfer of sensitive technologies, and companies typically do not disclose their intellectual property during standard discussions—therefore, in principle, Chinese participation in RISC-V does not mean access to advanced semiconductor technology.Importance of Continued Engagement with RISC-V: Efforts to force U.S. companies out of RISC-V will be counterproductive, as this will not prevent China and other companies from using RISC-V but will instead hand innovation over to Chinese companies. In fact, some U.S. companies still need to use RISC-V but will lose influence over its development. This could lead to fragmentation of the RISC-V ecosystem and potentially disadvantage U.S. companies, as they would have to develop multiple RISC-V systems without being able to influence the trajectory of ecosystem development. Moreover, U.S., European, and other companies supporting RISC-V have ample commercial and technical reasons. This allows them to avoid reliance on a single proprietary standard and benefit from a low-cost, adaptable, widely adopted, and continuously improving standard.Regulatory Limitations: An article from CSET in 2024 emphasized that, since RISC-V is managed by a Swiss standards organization, the U.S. has limited regulatory options regarding RISC-V; the only truly viable option is to restrict U.S. participation in RISC-V standardization. However, this move would backfire on U.S. companies (which might leave the U.S. to use RISC-V in other countries) and could undermine U.S. technological leadership and competitiveness.One of RISC-V’s main advantages is that it is a low-cost standard that researchers can leverage, teach and use in universities, and adopt by small startups and large companies. Importantly, RISC-V serves as a means to bring the innovative ideas of a new generation of researchers to market.The “Prospects and Paranoia of RISC-V” section of the 2021 report from the U.S. Institute for Foreign Policy Analysis looks at the longer-term future: the report argues that RISC-V holds many opportunities in adaptability and implementation, and the U.S. must invest heavily in RISC-V domestically to ensure its leadership in the open-source hardware space. The report notes that while some may be concerned about the rise of this new standard, the U.S. stands to benefit significantly. RISC-V will lower the cost of chip design and drive commoditization in certain areas of the chip industry, but it will also shift the focus of competition from capital to design innovation. This will fully leverage the U.S.’s current advantages in design and highlight the necessity of cultivating (or attracting) more high-end engineering talent and creating a favorable business environment for it.Crucially and challengingly, RISC-V has begun to integrate into the U.S. innovation ecosystem, applied in various projects in both the public and private sectors, such as NASA’s Jet Propulsion Laboratory’s space computing and Nvidia’s CUDA cores. One major advantage of RISC-V is that it is a low-cost standard that researchers can leverage, teach and use in universities, and adopt by small startups and large enterprises. It represents a more accessible, low-cost pathway to bring new innovative products and stronger competitiveness. More importantly, RISC-V serves as a means to bring the innovative ideas of a new generation of researchers to market.How to Move Towards Standard LeadershipHistorically, the U.S. has led in global standardization, promoting the growth and innovation of technology and its supply chains, providing advantages to U.S. companies. However, this focus has waned in recent years.China now recognizes the value of actively participating in standard-setting to develop its long-term competitive advantage. As emphasized in the “China Standards 2035” plan, China is prioritizing investment and participation in standard-setting organizations, aiming to win competitive advantages for Chinese companies across a wide range of emerging technologies. Abandoning standard leadership is not a wise move. In this context, the U.S. should actively take the lead and seize international standard-setting opportunities—including those presented by RISC-V. This requires the U.S. to focus on policy and invest more resources to participate in standard-setting organizations. The U.S. must recognize that China has changed the nature of standard competition, and it needs to take constructive and proactive measures in collaboration with like-minded countries.To move towards standard leadership, the U.S. can leverage existing projects and mechanisms within the semiconductor innovation ecosystem. To cultivate professionals proficient in RISC-V, the U.S. can further integrate RISC-V training into engineering curricula and workforce development, such as research scholar programs funded by semiconductor research companies. Additionally, RISC-V can be promoted in federally funded regional programs, such as the Department of Defense’s microelectronics public space and the Department of Commerce’s technology centers, in collaboration with universities, startups, and industry. Specifically, government-supported projects provide opportunities to support the necessary physical infrastructure to accelerate the development and validation of RISC-V across the ecosystem.The U.S. government needs to ensure that the National Institute of Standards and Technology (NIST) can actively participate in the international standard-setting process, including providing support for U.S. companies within standard-setting organizations like RISC-V International. NIST can also facilitate standard education by hosting workshops for government agencies and convening industry leaders to better understand their interests and challenges. Resources need to be provided to stakeholders to engage in international collaboration and develop standard strategies that best align with U.S. and like-minded countries’ interests. NIST’s work needs to be adequately funded and supported to ensure that U.S. companies, perspectives, and citizens are represented in this ongoing international standard-setting effort.ConclusionTo address this challenge, the U.S. should promote standard education, encourage research and development in the field, including engineering curricula, and provide adequate funding for U.S. participation.Encourage U.S. companies to actively participate in international standard-setting organizations and provide NIST with the necessary federal resources to balance China’s participation.Develop support for university and industry-based RISC-V research projects, especially to provide students with introductory training in RISC-V. Invest in building the physical infrastructure needed to support RISC-V development, including research and testing facilities for RISC-V hardware validation.Utilize existing mechanisms, such as the Semiconductor Research Corporation (SRC) mature programs, to support a cohort of professionals and projects proficient in RISC-V, including RISC-V electronic design automation tools. Talent development will be key.Emphasize the use and development of RISC-V in federally funded projects (such as the Department of Defense’s microelectronics shared center and other technology centers) as a means to connect researchers from industry and academia with tools and training to cultivate RISC-V leadership.RISC-V presents a critical strategic opportunity for the chip industry to lead and influence the global chip design field in the coming decades, but the necessary measures are urgent. The standard-setting process is like a moving train; we need to build a coalition to guide it, continue to support the entire domestic design industry, and advocate for investment and participation in RISC-V development.

In contrast, the latest entrant in the field is RISC-V (pronounced “risk five”), an open standard ISA based on RISC principles, which chip design teams can access and implement freely across various use cases without licensing restrictions. In other words, RISC-V allows for easy customization through royalty-free licenses and imposes no licensing restrictions on modifications.Global Platform: RISC-V was initially developed in 2010 at the Parallel Computing Laboratory at the University of California, Berkeley, and is now managed by the Swiss non-profit standards organization RISC-V International. This non-profit organization has attracted 4,600 members from 70 countries, including companies, universities, community organizations, and individuals collaborating on the development of the RISC-V ISA and its extensions. The Technical Advisory Board of RISC-V International includes U.S. entities (such as Google and Qualcomm) as well as Chinese organizations (such as Alibaba and Huawei). The 24 primary members of RISC-V International include startups, venture capital firms, and hyperscale companies, with 12 located in mainland China, 9 in the U.S., and one each in Taiwan, Brazil, and Spain. The board and overall membership are distributed across the U.S., China, and Europe, with the U.S. slightly leading in numbers.Flexibility and Accessibility: The flexibility and accessibility of RISC-V make it an extremely attractive and rapidly growing ISA. Early use cases have primarily focused on the embedded systems market, with potential applications in high-performance computing (HPC), artificial intelligence (AI), consumer electronics, and wearable devices. Currently, the number of RISC-V-based chips has exceeded 2 billion, and it is expected to grow to 20 billion by 2031. The membership of RISC-V International has increased from 236 in 2019 to over 4,600 by 2025, as the organization is committed to leveraging this support. At the end of 2019, escalating geopolitical tensions prompted RISC-V International’s management to move from Delaware to Switzerland, citing its mission to ensure that universities, governments, and businesses outside the U.S. can access and develop its technology. Since then, the non-profit organization has been building collaborative tools and opportunities within the ecosystem and has established 68 new specifications and over 80 working groups.Low-Cost, High-Control Platform: Many companies currently purchasing x86 or ARM ISA licenses are participating in the development of RISC-V to gain another semiconductor architecture option without paying high licensing fees. This allows engineers to build their implementations on top of the ISA, giving them better control over their technology and fully leveraging the software compatibility of the RISC-V ecosystem. For example, just five years after the launch of the RISC-V open standard ISA, Nvidia began transitioning from its proprietary microcontrollers to RISC-V-based cores in 2015. Other industry giants like Google, Qualcomm, and Samsung have taken similar steps. The customizable, low-cost ISA option is also attractive to small businesses.Secure IP Environment: It is important to emphasize again that RISC-V does not contain sensitive IP, and its collaborative development does not require companies to disclose such IP. The standardization of RISC-V does not require U.S. companies to share confidential information with others. Companies’ sensitive IP is only used for their RISC-V implementations and is not shared through the RISC-V platform itself, and companies can license their RISC-V implementations. For instance, startups like SiFive and Tenstorrent use the RISC-V ISA and then license their implementations as IP. Additionally, some believe that open-source ISA designs are more secure than closed designs because they allow members of the tech community to collaboratively identify vulnerabilities.The standardization of RISC-V does not require U.S. companies to share confidential information with others. Companies’ sensitive IP is only used for their RISC-V implementations and is not shared through the RISC-V platform itself, and companies can license their RISC-V implementations.The Business Case for RISC-VRapid Industry Adoption: According to BCC Publishing, the market revenue for RISC-V technology is expected to grow at a compound annual growth rate of 33.1% from 2022 to 2027. The U.S. Defense Advanced Research Projects Agency (DARPA) supported the development of RISC-V multicore processors in 2018. By 2025, many U.S. companies are rapidly investing in RISC-V-based software implementations, from microcontrollers in Nvidia’s GPUs to Samsung’s 5G mmWave RF and Seagate’s HDD controllers. In fact, in May 2023, industry leaders and startups collaborated to launch the RISC-V Software Ecosystem (RISE) project, aimed at accelerating the integration of RISC-V software into consumer electronics, data centers, and automotive products. RISE’s 13 senior members and 10 regular members include Google, Intel, Nvidia, Qualcomm, Red Hat, Rivos, SiFive, Ventana, Samsung, MediaTek, ByteDance, and Tenstorrent.Major industry players have also publicly described the increasingly important role of the RISC-V architecture in AI applications and scaling. In 2018, Google co-founded OpenTitan, aimed at developing an open-source, root-of-trust chip, which has received support from community members as well as industry and academic partners. Qualcomm has used RISC-V cores in some of its Snapdragon processors, with over 650 million such cores shipped. Nvidia revealed in October 2024 that its custom CUDA cores will be based on the RISC-V ISA standard. To date, the company has developed at least three RISC-V microcontroller cores, with expected shipments reaching 1 billion by October 2024.Greater Technical Flexibility: Why are so many companies investing in RISC-V? The answer boils down to flexibility and cost, primarily reflected in supply chain and customizability aspects. Licensing requirements are expensive and fraught with restrictions, not to mention the legal complexities involved. Additionally, RISC-V is currently more technically flexible than earlier ISAs. For example, x86 has undergone long iterations, continually adding extensions and complexity, making it difficult to apply to new applications. RISC-V-based cores do not carry the legacy issues of previous generations and can be more easily customized for performance advantages or higher compute density. As a spokesperson from Ventana Micro explained, “Adding an instruction in RISC-V is a relatively simple process; you just propose the instruction definition, provide the justification needed for the instruction, and have it reviewed by the RISC-V International Technical Advisory Board.”While the recent developments of RISC-V have brought many advantages, its emerging characteristics also mean it does not have the same level of technical and customer support networks as proprietary ISAs. ARM’s proprietary technology comes with support and liability guarantees, while RISC-V International is currently working to build that ecosystem. As a spokesperson from Ventana Micro explained, “Our goal has always been to drive all new instructions/extensions through RISC-V International to prevent industry fragmentation. Even so, if you do need to get something done, you can always push it through quickly and incubate accelerated ideas on a common basis. This is precisely why RISC-V is attracting so many AI applications.”Increasing Adoption of RISC-VRISC-V is not only a competitor to x86 and ARM but also represents a groundbreaking alternative for a wide range of current and potential applications in chip design.Current Applications: Currently, RISC-V is primarily applied in embedded technology, with broad market prospects in wearable devices, global automotive, and HPC/AI industries. The fabless company SiFive is an early supporter of RISC-V high-performance chips, with its chips used in Google data centers and NASA’s high-performance space computers. RISC-V is also used to build flexible chips that power wearable medical electronics, smart packaging tags, soft robotics, and other low-cost products.Future Applications: While RISC-V may not compete with x86 and ARM in mainstream consumer electronics applications for at least a decade, leading companies are already using RISC-V to develop future capabilities. Alibaba is developing RISC-V chips for edge computing, and Hong Kong-based DeepComputing has released the world’s first RISC-V laptop, although its performance currently lags behind laptops using proprietary ISAs. In 2024, engineers from Intel’s Advanced Architecture Development Division founded AheadComputing Inc., a startup focused on developing RISC-V core IP.Infrastructure Needs: Crucially, for RISC-V to become a mainstay in mainstream devices, a robust ecosystem of tools, support systems, and resources must be built to attract chip manufacturers and producers. RISC-V International approved the RVA23 specification in October 2024, marking an important milestone; this specification is a set of standardized ISA extensions compatible with RISC-V, although much work remains to support its development ecosystem.RISC-V as a Strategic Opportunity for U.S. Standard Innovation LeadershipGiven the rapid proliferation of the RISC-V platform and its advantages in enhancing interoperability and collaboration, what are the policy options for the U.S.? Recent analyses have highlighted considerations for U.S. policymakers regarding RISC-V policy:Need for Better Understanding of RISC-V: A 2024 review noted that policymakers do not sufficiently understand RISC-V—especially that chip competition occurs at the implementation level, not the standard level. This means that each company implements the ISA in unique ways and independently adds its proprietary innovations. In short, RISC-V does not involve the transfer of sensitive technologies, and companies typically do not disclose their intellectual property during standard discussions—therefore, in principle, Chinese participation in RISC-V does not mean access to advanced semiconductor technology.Importance of Continued Engagement with RISC-V: Efforts to force U.S. companies out of RISC-V will be counterproductive, as this will not prevent China and other companies from using RISC-V but will instead hand innovation over to Chinese companies. In fact, some U.S. companies still need to use RISC-V but will lose influence over its development. This could lead to fragmentation of the RISC-V ecosystem and potentially disadvantage U.S. companies, as they would have to develop multiple RISC-V systems without being able to influence the trajectory of ecosystem development. Moreover, U.S., European, and other companies supporting RISC-V have ample commercial and technical reasons. This allows them to avoid reliance on a single proprietary standard and benefit from a low-cost, adaptable, widely adopted, and continuously improving standard.Regulatory Limitations: An article from CSET in 2024 emphasized that, since RISC-V is managed by a Swiss standards organization, the U.S. has limited regulatory options regarding RISC-V; the only truly viable option is to restrict U.S. participation in RISC-V standardization. However, this move would backfire on U.S. companies (which might leave the U.S. to use RISC-V in other countries) and could undermine U.S. technological leadership and competitiveness.One of RISC-V’s main advantages is that it is a low-cost standard that researchers can leverage, teach and use in universities, and adopt by small startups and large companies. Importantly, RISC-V serves as a means to bring the innovative ideas of a new generation of researchers to market.The “Prospects and Paranoia of RISC-V” section of the 2021 report from the U.S. Institute for Foreign Policy Analysis looks at the longer-term future: the report argues that RISC-V holds many opportunities in adaptability and implementation, and the U.S. must invest heavily in RISC-V domestically to ensure its leadership in the open-source hardware space. The report notes that while some may be concerned about the rise of this new standard, the U.S. stands to benefit significantly. RISC-V will lower the cost of chip design and drive commoditization in certain areas of the chip industry, but it will also shift the focus of competition from capital to design innovation. This will fully leverage the U.S.’s current advantages in design and highlight the necessity of cultivating (or attracting) more high-end engineering talent and creating a favorable business environment for it.Crucially and challengingly, RISC-V has begun to integrate into the U.S. innovation ecosystem, applied in various projects in both the public and private sectors, such as NASA’s Jet Propulsion Laboratory’s space computing and Nvidia’s CUDA cores. One major advantage of RISC-V is that it is a low-cost standard that researchers can leverage, teach and use in universities, and adopt by small startups and large enterprises. It represents a more accessible, low-cost pathway to bring new innovative products and stronger competitiveness. More importantly, RISC-V serves as a means to bring the innovative ideas of a new generation of researchers to market.How to Move Towards Standard LeadershipHistorically, the U.S. has led in global standardization, promoting the growth and innovation of technology and its supply chains, providing advantages to U.S. companies. However, this focus has waned in recent years.China now recognizes the value of actively participating in standard-setting to develop its long-term competitive advantage. As emphasized in the “China Standards 2035” plan, China is prioritizing investment and participation in standard-setting organizations, aiming to win competitive advantages for Chinese companies across a wide range of emerging technologies. Abandoning standard leadership is not a wise move. In this context, the U.S. should actively take the lead and seize international standard-setting opportunities—including those presented by RISC-V. This requires the U.S. to focus on policy and invest more resources to participate in standard-setting organizations. The U.S. must recognize that China has changed the nature of standard competition, and it needs to take constructive and proactive measures in collaboration with like-minded countries.To move towards standard leadership, the U.S. can leverage existing projects and mechanisms within the semiconductor innovation ecosystem. To cultivate professionals proficient in RISC-V, the U.S. can further integrate RISC-V training into engineering curricula and workforce development, such as research scholar programs funded by semiconductor research companies. Additionally, RISC-V can be promoted in federally funded regional programs, such as the Department of Defense’s microelectronics public space and the Department of Commerce’s technology centers, in collaboration with universities, startups, and industry. Specifically, government-supported projects provide opportunities to support the necessary physical infrastructure to accelerate the development and validation of RISC-V across the ecosystem.The U.S. government needs to ensure that the National Institute of Standards and Technology (NIST) can actively participate in the international standard-setting process, including providing support for U.S. companies within standard-setting organizations like RISC-V International. NIST can also facilitate standard education by hosting workshops for government agencies and convening industry leaders to better understand their interests and challenges. Resources need to be provided to stakeholders to engage in international collaboration and develop standard strategies that best align with U.S. and like-minded countries’ interests. NIST’s work needs to be adequately funded and supported to ensure that U.S. companies, perspectives, and citizens are represented in this ongoing international standard-setting effort.ConclusionTo address this challenge, the U.S. should promote standard education, encourage research and development in the field, including engineering curricula, and provide adequate funding for U.S. participation.Encourage U.S. companies to actively participate in international standard-setting organizations and provide NIST with the necessary federal resources to balance China’s participation.Develop support for university and industry-based RISC-V research projects, especially to provide students with introductory training in RISC-V. Invest in building the physical infrastructure needed to support RISC-V development, including research and testing facilities for RISC-V hardware validation.Utilize existing mechanisms, such as the Semiconductor Research Corporation (SRC) mature programs, to support a cohort of professionals and projects proficient in RISC-V, including RISC-V electronic design automation tools. Talent development will be key.Emphasize the use and development of RISC-V in federally funded projects (such as the Department of Defense’s microelectronics shared center and other technology centers) as a means to connect researchers from industry and academia with tools and training to cultivate RISC-V leadership.RISC-V presents a critical strategic opportunity for the chip industry to lead and influence the global chip design field in the coming decades, but the necessary measures are urgent. The standard-setting process is like a moving train; we need to build a coalition to guide it, continue to support the entire domestic design industry, and advocate for investment and participation in RISC-V development.