RISC-V as an open-source Instruction Set Architecture (ISA) has rapidly risen globally in recent years, promising to reshape the semiconductor industry landscape. From chip design companies to software developers, from academic research institutions to industry giants, there is active exploration of RISC-V applications and innovations.

Omdia reported that in the past three years, an increasing number of RISC manufacturers have entered the RISC-V space, with processors and accelerators based on RISC-V technology growing at an astonishing rate, achieving a compound annual growth rate (CAGR) of 75% from 2020 to 2024. By 2030, Omdia expects the annual growth rate to remain close to 50%, which translates to an approximate annual growth rate of 57% over the decade from 2020 to 2030.

In this trend, industry chain enterprises are rushing into the RISC-V track. As one of the few companies in China with full-stack R&D capabilities for server-level high-performance processors, Beijing Microcore Technology Co., Ltd. (hereinafter referred to as “Microcore”) is deeply engaged in the RISC-V architecture, leveraging technological innovation and ecosystem development to help the Chinese chip industry achieve a leapfrog development.

Choosing RISC-V: The Innovative Path to Breaking Monopolies

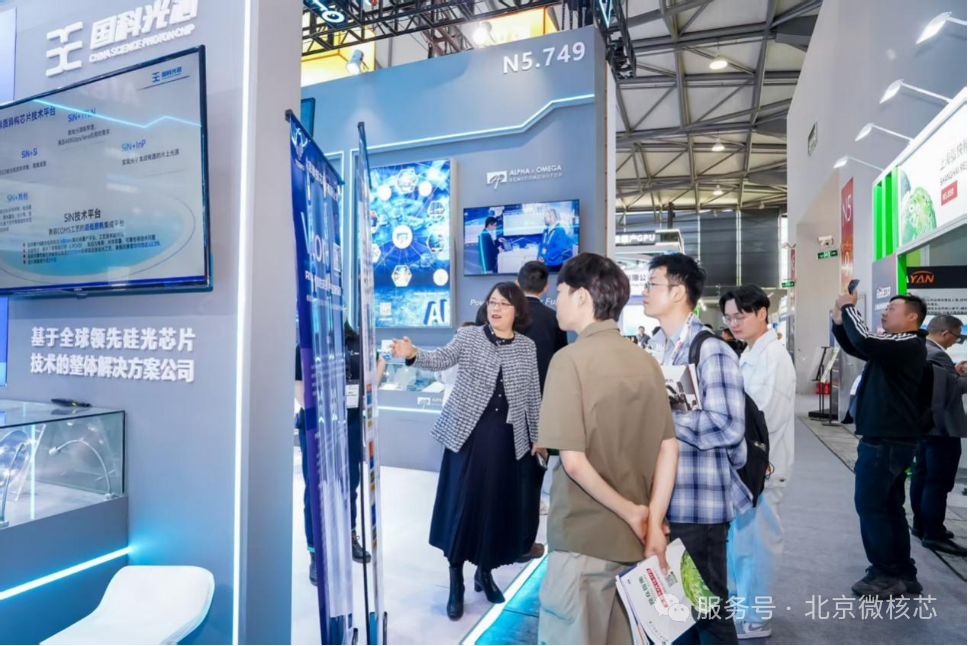

If we only focus on low-end IoT chips, we cannot shake the ecological status of X86 and ARM. During the 2025 Munich Shanghai Electronics Show, Microcore CEO Xuandan told the media that high-performance computing scenarios are key to unlocking the RISC-V market space. “In the past, RISC-V was mostly aimed at the AIoT field, where low-cost and low-performance areas have become a red ocean market. For the emerging RISC-V industry to grow and thrive, it must grow alongside new applications in high-performance areas (servers, AI computing) in data centers to unlock market space.”

Unlike the “general redundancy” of traditional X86 and ARM, the microarchitecture of the RISC-V instruction set can achieve modular scalability on an open ecosystem basis and integrate with industry-level applications, providing high flexibility and customization advantages. It will not become a limitation or constraint for enterprises like other proprietary instruction sets, but rather become the key for enterprises to gain control over their own software and hardware collaborative development.

“We are always optimistic about the open-source RISC-V instruction set because it can create an industrial synergy for the development of Chinese processors.” Xuandan stated. The advantages of RISC-V compared to traditional instruction sets are:

1. A new ecosystem that is open-source and neutral;

2. Market and ecosystem jointly define standards;

3. Freedom of definition and innovation from instruction to microarchitecture/IP to chip to software.

“In the future, there will be such demand across various industries, and the market space is enormous. We believe that the most suitable entry point for RISC-V in the data center server field is to first enter the industry application market and then enter the public cloud field in a general way.”

Technical Breakthrough: Architectural Innovation Compensates for Process Limitations

While international giants compete for 3nm processes, Microcore chooses to focus on the domestically controllable processes of 12/7nm, which are “two generations behind.” The secret lies in “deep optimization across multiple levels including instruction set, microarchitecture, high-speed interconnect, SoC framework, and software optimization, using ‘hardware acceleration’ to replace the ‘software acceleration’ of general processors, achieving a better cost-performance ratio or performance-to-power ratio than ARM/X86 under supply chain constraints.” Xuandan said, “This is something that ARM/X86 cannot achieve.”

Currently, Microcore’s high-performance processor core performance can match that of ARM’s server-side processor N2. Xuandan introduced: “From the technical route of servers, we develop high-performance processors based on controllable processes to ensure the feasibility of mass production later, gradually deepening the customized design of key modules to solve the performance bottlenecks of server chips, reaching the performance level of internationally advanced processors. We provide a complete server system solution, including high-performance CPU cores + NoC multi-core interconnect + SoC architecture, combined with Chiplet technology to reduce the design and manufacturing costs of server chips and accelerate the iteration speed of chip R&D.”

In terms of architectural innovation, leveraging Microcore’s technical team’s full-stack self-research capabilities and experience in deep integration with applications, Microcore covers all areas of high-performance processor development, including processor architecture design, verification, physical implementation, and the entire software process, achieving self-research in processor cores + multi-core interconnect NoC + SoC. Single-core performance reaches 15 points/GHz, equivalent to the performance level of ARM server-grade processor cores. NoC supports multi-core processor interconnect, with hardware support for cache coherence and CHI protocol multi-core scalability.

Furthermore, by utilizing a high-performance processor agile development platform that encompasses the entire chip development process, the processor is decomposed into various parameter-configurable and adjustable standardized modules, which have been pre-implemented for high performance. “Thus, based on this agile development platform, we can optimize and trim at the microarchitecture level according to application needs, enabling rapid modifications, rapid validations, and rapid implementations, minimizing the chip design cycle and accelerating the time to market for chips.”

Commercialization: Doing What X86/ARM Want to Do but Cannot

China currently faces the reality of supply chain blockades, which also presents an opportunity for the development of the Chinese RISC-V industry. “Supply chain constraints mean that we must continuously refine our chip design and implementation capabilities based on market demand.” Xuandan pointed out, “The RISC-V platform is very suitable for deep integration with enterprise applications, allowing users to fully grasp their power to define future software and hardware architectures.”

However, commercialization is one of the biggest challenges faced by RISC-V companies. Microcore’s strategy is to “deeply integrate with applications to do what X86 and ARM want to do but cannot.”

In Xuandan’s view, the challenges of RISC-V commercialization lie in two key aspects: building ecological confidence and breaking through differentiated tracks. On one hand, it requires establishing enterprise confidence in the RISC-V industry, relying on mutual assistance in the ecological environment, technical verification, and policy guidance, among other measures; on the other hand, it is necessary to find an industry opportunity where RISC-V can enter and outperform X86/ARM, such as in the high-performance segment of data centers, especially in servers and AI computing, where RISC-V architecture processors possess openness and modular design, making them well-suited for various usage scenarios while providing efficient and low-cost solutions.

“For us, creating an open custom platform, ensuring sufficient demand and market space, and optimizing the results for this application field, we believe it has considerable market competitiveness.” Xuandan stated.

Microcore not only focuses on the R&D of high-performance chips but also provides a full set of solutions for industry clients, from instruction set optimization, microarchitecture adjustments to software adaptation through customized services. Currently, Microcore has three series of processor cores that can be commercially delivered, with SPEC CPU2006 scores of 10 points/GHz, 13 points/GHz, and 15 points/GHz, corresponding to ARM A78, ARM N1, and N2. “Through a customized model, we can select or further optimize based on user needs, deeply integrating with users to jointly define and optimize chip design, thus achieving a more optimized cost-performance ratio or performance-to-power ratio.”

Microcore’s market strategy also reflects its emphasis on ecosystem construction. The company is gradually building the RISC-V industry application ecosystem through cooperation with several leading internet companies in storage servers and DPU fields, starting from specific industry areas and then entering the public cloud field.

Looking to the Future: Deep Integration of AI and RISC-V

In the era of artificial intelligence, Microcore is also actively exploring the deep integration of RISC-V and AI. They believe that RISC-V and AI are similar in that they are both universal technologies, and once deeply integrated with applications, they can unleash infinite power. From the perspective of basic computing power and ecosystem construction, under supply chain constraints, what we hope to achieve is a deep integration of AI with specific application scenarios.

Microcore’s AI layout focuses on emerging fields such as autonomous driving and robotics, where these application scenarios demand high comprehensive performance, power consumption, and response speed from chips, requiring high energy efficiency and low-latency computing power. RISC-V high-performance processors are currently a relatively new and hot direction.

Xuandan believes that the development of AI chips in China needs to reasonably optimize custom chips based on application needs, balancing between extreme generality and extreme specificity. Achieving this balance requires not only a profound understanding of chip architecture but also an accurate grasp of application needs.

The combination of CPU and AI (or GPGPU) is key to future chip design, where the CPU mainly executes control flow, while AI or GPGPU mainly executes data flow. In practical applications, it is often a combination of both, requiring optimization based on different application scenarios. To achieve efficient chip system solutions, it is essential to deeply integrate application needs with chip design, especially to design a good collaborative framework between CPU and AI. Furthermore, hardware-software co-design is crucial, requiring in-depth decomposition and optimization of application needs, computing frameworks, data flow, and control flow from the application perspective.

To this end, Microcore proposes a three-tier CPU+AI collaborative framework:

1) Integration of AI acceleration modules within the SoC framework: AI has high execution efficiency but poor adaptability to future applications and weak integration with control flow, only interacting with the CPU at the memory level.

2) AI instruction extensions at the CPU level: Best adaptability to applications but lowest AI execution efficiency, suitable for special application areas where control flow is dominant and data flow is secondary.

3) Design of AI coprocessors within the CPU framework: Combining the control flow execution capabilities of high-performance CPUs with the high execution efficiency of AI coprocessors, this is the trend for future AI chip development.

Microcore believes that the third solution can better balance the processing needs of control flow and data flow, making it the core direction for future AI chip design. Moreover, based on the third solution, it can also combine with the other two solutions to adapt to different application fields.

The association provides a platform for enterprises to showcase and collaborate. Enterprises in need can contact member teachers. Thank you for your participation! For more information, follow the High-tech Enterprise AssociationPlease mark it as a star ★to check the latest policy information and more exciting content in a timely manner!

For more information, follow the High-tech Enterprise AssociationPlease mark it as a star ★to check the latest policy information and more exciting content in a timely manner!