23. Internal Structure and Resources of FPGA:

FPGA mainly consists of programmable units, programmable I/O units, and wiring resources. The programmable logic unit (Configurable Logic Block, CLB) consists of two slices, where slices mainly include LUTs for implementing combinational logic and flip-flops for implementing sequential logic. FPGA also contains dedicated storage units like BRAM, DSP slices for computation, and dedicated embedded functional units such as PLL, Serdes, etc.

24. Define Terms and Write the Meanings of the Following Abbreviations::

FPGA: Field Programmable Gate Array

VHDL: Very-High-Speed Integrated Circuit Hardware Description Language

HDL: Hardware Description Language

EDA: Electronic Design Automation

CPLD: Complex Programmable Logic Device

PLD: Programmable Logic Device

GAL: Generic Array Logic

LAB: Logic Array Block

CLB: Configurable Logic Block

EAB: Embedded Array Block

SOPC: System-on-a-Programmable-Chip

LUT: Look-Up Table

JTAG: Joint Test Action Group

IP: Intellectual Property

ASIC: Application Specific Integrated Circuits

ISP: In System Programmable

ICR: In Circuit Re-configurable

RTL: Register Transfer Level

25. Principles of How LUT Implements Combinational Logic:

LUT is equivalent to a RAM storing the truth table corresponding to the logic expression. The software lists all possible results of the logic expression and stores them in RAM, using inputs as RAM addresses and outputs as logical operation results. For example, using LUT to simulate two-input AND logic. The truth table is: 00 – 0, 01 – 0, 10 – 0, 11 – 1. At this time, 00, 01, 10, 11 are used as address lines, and the results 0, 0, 0, 1 are stored in RAM in sequence. When input 00, the output is 0 & 0 = 0.

26. Low Power Consumption Techniques:

Power consumption can be described by the formula: Power = KFCV^2, meaning power equals the constant coefficient times frequency times load capacitance times the square of voltage. Hence, methods to reduce power consumption include:

1. Control operating frequency: reduce frequency, increase data path width, dynamically adjust frequency, and gate clock (effective clock only enters the register clock input pin when enabled).

2. Reduce capacitive load: use smaller logic gates whose capacitive loads are smaller, which also reduces power consumption.

3. Reduce operating voltage: dynamically change operating voltage and zero operating voltage (directly shut down part of the power supply in the system).

27. Basic Concepts of MOS Transistor and Drawing:

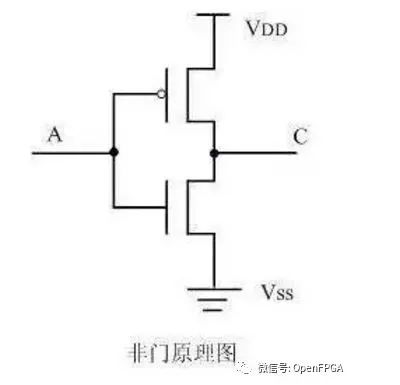

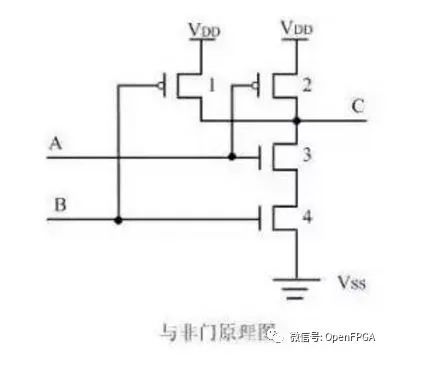

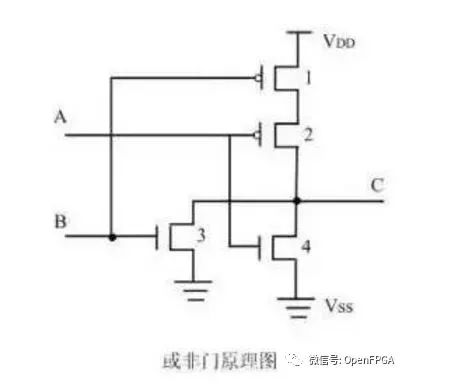

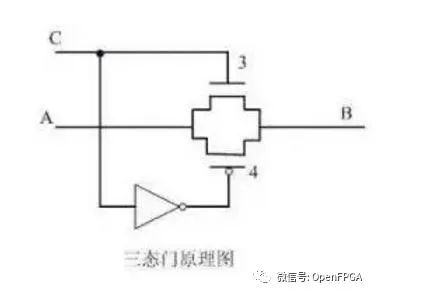

MOS (Metal-Oxide-Semiconductor) transistor consists of gate (G), drain (D), and source (S). There are two types: PMOS and NMOS, differentiated by the fact that when the gate level is high, the N-type transistor conducts, and the P-type transistor is off. They often appear in pairs, known as CMOS. As long as one conducts, the other is off. Modern microcontrollers are mainly made using CMOS technology. Drawing typically requires a simple logic expression to illustrate the CMOS circuit structure. It is necessary to master the implementation methods of commonly used logic gates.

Overall, it is quite memorable that both NAND and NOR gates consist of two MOS transistors each, with the upper being PMOS and the lower being NMOS. The difference lies in the fact that NAND is “upper parallel and lower series” while NOR is “upper series and lower parallel.”

28. Detailed FPGA Design Process (Interview Questions)

Similar to the digital IC design process, taking Xilinx Vivado tools as an example, the main steps are: system planning, RTL input, behavioral simulation, logic synthesis, post-synthesis simulation (optional), post-synthesis design analysis (timing and resources), design implementation (including layout and routing optimization), post-implementation design analysis (timing and resources), board-level debugging, and bitstream solidification.

29. What Timing Paths Are Related to Timing Constraints?

Input paths: External pins to internal registers.

Register-to-register paths: Internal register to register paths.

Output paths: Internal registers to external pins.

Port to port paths: FPGA input port to output port paths (not commonly used).

30. Key Steps in Creating Timing Constraints:

Baseline constraints: create clocks, define clock interactions.

I/O constraints: set input and output delays.

Exception constraints: set timing exceptions (set_max_delay/set_min_delay, set_multicycle_path, set_false_path).

Initially, I/O constraints can be omitted, but baseline constraints should be established as early as possible.

31. Differences Between SRAM and DRAM:

SRAM is static random-access memory, storing data with transistors, requiring no refresh, and has fast read/write speeds.

DRAM is dynamic random-access memory, storing data with capacitors, requiring dynamic refresh due to capacitor leakage, and has slower read/write speeds than SRAM but lower costs, suitable for large-capacity external caching.

32. What Are the Differences Between CMOS and TTL Circuits?

The differences mainly lie in three aspects:

Structure: CMOS circuits are made of field-effect transistors, while TTL is made of bipolar transistors.

Voltage Range: CMOS logic has a larger voltage range (5~15V), while TTL operates below 5V, so CMOS has greater noise tolerance and stronger anti-interference ability.

Power Consumption and Speed: CMOS consumes less power than TTL but has a lower operating frequency.

TTL cannot directly drive CMOS levels without a pull-up resistor, while CMOS can directly drive TTL.

33. JTAG Interface Signals and Functions:

JTAG actually uses only four signals: Clock TCK, State Machine Control Signal TMS, Data Input Signal TDI, and Data Output Signal TDO.

34. Uses of Pull-Up Resistors:

1. When a TTL circuit drives a CMOS circuit, if the high level output from the TTL circuit is below the minimum high level of the CMOS circuit (generally 3.5V), a pull-up resistor is needed at the TTL output to increase the output high level value.

2. OC gate circuits must have pull-up resistors to increase the output high level value.

3. To increase the driving capability of output pins, some microcontroller pins often use pull-up resistors.

4. In CMOS chips, to prevent damage from static electricity, unused pins should not be left floating; they are usually connected to pull-up resistors to lower input impedance and provide a discharge path.

5. Adding pull-up resistors to chip pins increases output levels, thus enhancing noise tolerance and anti-interference ability.

6. Increases the bus’s resistance to electromagnetic interference. Floating pins are more susceptible to external electromagnetic interference.

7. In long line transmission, impedance mismatch can easily cause reflection wave interference; adding pull-up resistors matches impedance, effectively suppressing reflection wave interference.

35. There Are Four Multiplexing Methods, Write Out the Other Three Besides Frequency Division Multiplexing:

Four multiplexing methods: Frequency Division Multiplexing (FDMA), Time Division Multiplexing (TDMA), Code Division Multiplexing (CDMA), and Wavelength Division Multiplexing (WDM).

36. What Is Kirchhoff’s Theorem?

Kirchhoff’s laws include the current law and the voltage law:

Current Law: In a lumped circuit, at any given moment, the sum of currents flowing into a node equals the sum of currents flowing out of that node.

Voltage Law: In a lumped circuit, at any given moment, the sum of electromotive forces around any closed loop equals the sum of voltage drops across the resistors in that loop.

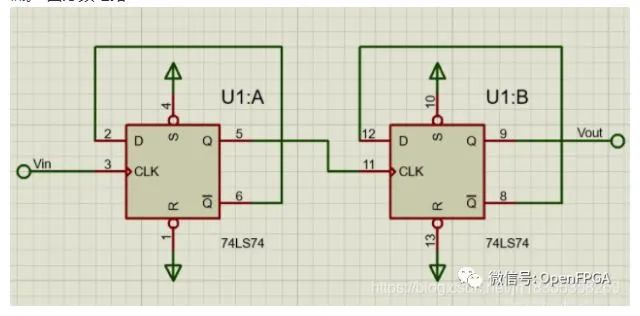

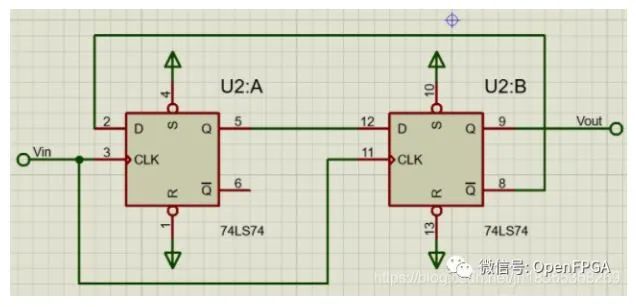

37. Three-Stage State Machine:

One-stage: Only one always block, implementing all logic (inputs, outputs, states) in a single always block’s sequential logic. This approach appears concise but is not maintainable; if the state is complex, it is easy to make mistakes and is not recommended. It can be used in simple state machines.

Two-stage: There are two always blocks, separating sequential logic and combinational logic. The sequential logic handles the transition between the current state and the next state, while the combinational logic implements inputs, outputs, and state judgments. This approach not only facilitates reading, understanding, and maintenance but also aids the synthesizer in optimizing code and allows users to add suitable timing constraints, benefiting layout and routing. In two-stage descriptions, the output of the current state is implemented using combinational logic, which may lead to races and hazards, producing glitches.

It is required that the outputs of the state machine be registered with a clock pulse, but in many cases, inserting a registered pulse is not allowed. In such cases, a three-stage description is used. Its advantage is that it can determine the current state’s output based on the state transition rules from the previous state according to input conditions, thus eliminating the need to insert extra clock pulses.

Three-stage: There are three always blocks, one for sequential logic describing state transitions using synchronous timing, one for combinational logic determining state transition conditions and describing state transition rules, and the third module using synchronous timing to describe the output of each state. The code is easier to maintain, and the output of the sequential logic solves the glitches from the combinational logic in the two-stage approach, but from a resource consumption perspective, the three-stage approach consumes more resources. The main difference between the two-stage and three-stage methods is whether the output of each state is implemented using combinational logic or sequential logic; combinational logic may lead to races and hazards, producing glitches.

38. What Is a State Diagram?

A state diagram describes the state transition rules of a sequential logic circuit and the relationship between outputs and inputs using geometric shapes.

39. Design a 7-bit Presettable Counter Using a Design Method You Are Familiar With, What About 15-bit?

module counter7(clk, rst, load, data, cout);

always@(posedge clk) begin

40. What Programmable Logic Devices Do You Know?

PAL, PLA, GAL, CPLD, FPGA.

41. Differences Between SRAM, FLASH MEMORY, DRAM, SSRAM, and SDRAM?

SRAM: Static Random Access Memory, fast access speed, but small capacity, data is lost after power off, unlike DRAM which requires constant REFRESH, and has higher manufacturing costs, usually used as cache memory.

FLASH: Flash memory, slower access speed, large capacity, data is retained after power off.

DRAM: Dynamic Random Access Memory, must constantly refresh the voltage difference, otherwise the voltage difference will drop to insufficient energy to represent the state of each memory unit. It is cheaper than SRAM but has slower access speeds and higher power consumption, commonly used as computer memory.

SSRAM: Synchronous Static Random Access Memory. All accesses to SSRAM are initiated on the rising/falling edge of the clock. Address, data input, and other control signals are all related to the clock signal.

SDRAM: Synchronous Dynamic Random Access Memory.

42. Differences Between Active and Passive Filters:

Passive filters: These circuits mainly consist of passive components R, L, and C.

Active filters: Composed of integrated operational amplifiers and R, C, they have advantages such as no need for inductors, small size, and lightweight. The open-loop voltage gain and input impedance of integrated operational amplifiers are both high, and they have a small output impedance, providing voltage amplification and buffering when forming active filter circuits. However, the bandwidth of integrated operational amplifiers is limited, making it difficult for current active filter circuits to operate at high frequencies.

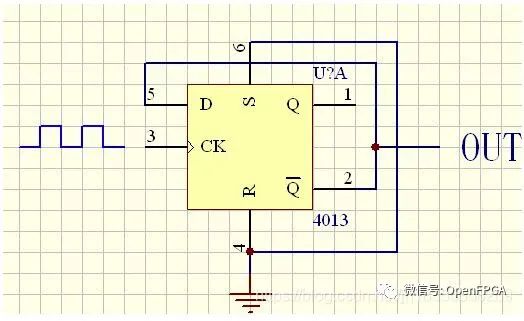

43. What Are Synchronous Logic and Asynchronous Logic?

Synchronous sequential logic circuits have the characteristic that all flip-flops’ clock terminals are connected together and to the system clock terminal; the circuit’s state can only change when the clock pulse arrives. The changed state will remain until the next clock pulse arrives, making every state in the state table stable regardless of external input changes.

Asynchronous sequential logic circuits can use clocked flip-flops as well as flip-flops and delay elements without clocks as storage elements, with no unified clock in the circuit; changes in circuit states are directly caused by changes in external inputs. Synchronous logic has a fixed causal relationship between clocks, while asynchronous logic does not.

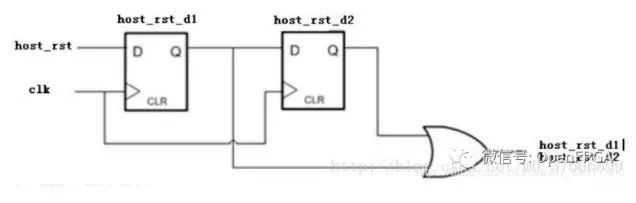

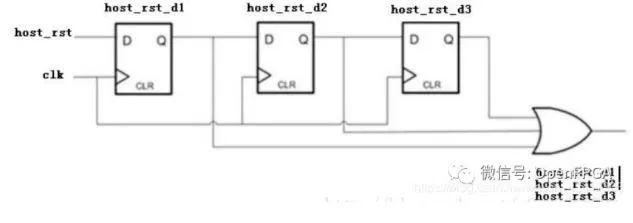

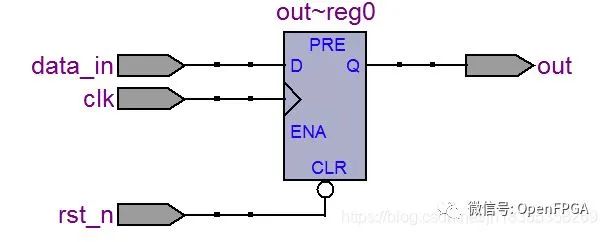

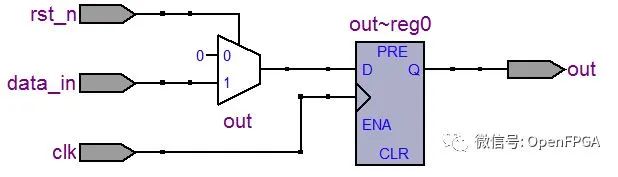

44. Differences Between Synchronous Reset and Asynchronous Reset:

Synchronous reset is performed when the clock edge changes.

Advantages: 1) High anti-interference ability, can filter out glitches in the reset signal with periods shorter than the clock period; 2) Beneficial for static timing analysis tools; 3) Beneficial for clock-based simulation tools.

Disadvantages: 1) Occupies more resources; 2) Requires the pulse width of the reset signal to exceed the clock period due to line delays; it may require multiple clock cycles of reset pulse width, and it is difficult to ensure the timing of the reset signal reaches each register; 3) Synchronous reset depends on the clock; if there are issues with the clock signal in the circuit, it cannot reset.

Asynchronous reset completes the reset action as long as the reset signal meets the conditions.

Advantages: 1) Does not require additional logic resources, simple implementation; 2) The reset signal is independent of the clock.

Disadvantages: 1) The reset signal is easily affected by external interference and sensitive to glitches in the circuit; 2) The randomness of the reset signal may lead to timing violations, meaning that when the reset signal is released near the clock valid edge, it can put the circuit into a metastable state.

45. What Two Types of Storage Resources Are Available in FPGA Chips?

FPGA chips have two types of storage resources: one called block RAM, and the other is internal memory configured by LUT (distributed RAM). Block RAM consists of a certain number of fixed-size storage blocks, and using BLOCK RAM resources does not occupy additional logic resources and is fast. However, when using it, the consumption of BLOCK RAM resources is an integer multiple of its block size.

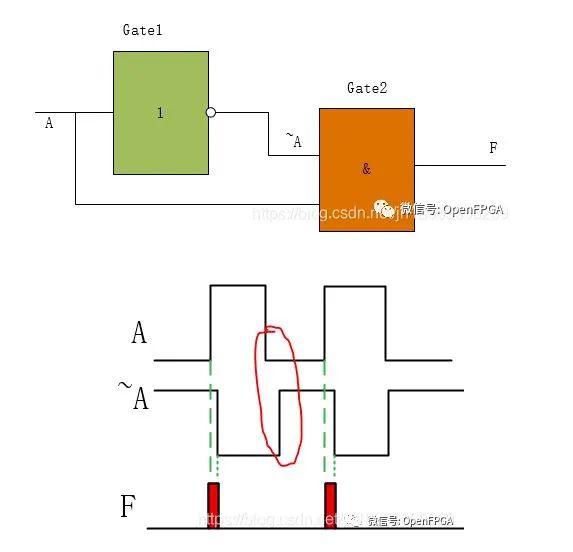

46. What Are Race and Hazard Phenomena? How to Judge? How to Eliminate?

Race: In combinational logic, when the input signal paths to the gate have different delays, resulting in inconsistent arrival times at that gate, it is called a race condition.

Hazard: The instantaneous error caused by a race condition is called a hazard (the glitches caused by races are called hazards).

Judgment methods: 1) Algebraic method: If there are opposing signals in the Boolean expression, it is likely to produce race and hazard phenomena; 2) Graphical method: If there are two tangent Karnaugh maps and the tangential point is not surrounded by other Karnaugh maps, there is a possibility of race and hazard phenomena; 3) Experimental method: Using an oscilloscope for observation.

Solutions: 1) Add filtering circuits to eliminate glitch effects; 2) Add selective signals to avoid glitches; 3) Add or reduce redundant terms to eliminate logical hazards.

☞ Business Cooperation: ☏ Please call 010-82306118 / ✐ Or send an email to [email protected]

Click here to read the original text, directly to Electronic Technology Application Official Website