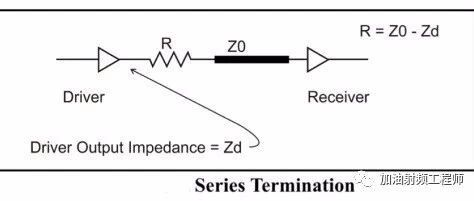

Why Add 22 or 33 Ohm Resistors to SPI Signal Outputs?

For more experience sharing, follow RF Engineer When a microcontroller or FPGA sends SPI control signals to a phase-locked loop chip, it often requires a series connection of a 22 ohm or 33 ohm resistor. What is the reason for this? Impedance discontinuities can cause electromagnetic wave reflections, which in turn lead to signal distortion. … Read more