Welcome FPGA engineers to join the official WeChat technical group

Clickthe blue textto follow us at FPGA Home – the largest and best community for pure FPGA engineers in China

Introduction:

Can be started at any time, can be restarted, the delay duration is adjustable, and the unit can be switched (ms/us). The delay range under a 50MHz clock is 1ms-85899ms/1us-85899us.

Source code and ModelSim simulation code:

module delay

//#(parameter N ) // Delay for N*1ms/us

(input clk,rst_n,

input start, // Rising edge of start is valid

input delay_unit, // Delay unit, high:ms/low:us

output finish,finish_pose); // Rising edge of finish is valid

reg start_reg0,start_reg1; // Two-stage buffer for start, used for edge detection

reg finish_reg0,finish_reg1; // Two-stage buffer for finish

reg [31:0]cnt; // Fixed 32-bit wide counter

reg [31:0]cnt_full;

reg restart; // Restart

wire start_pose,full;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt <= 32’d0;

cnt_full <= 32’d10; // Avoid finishing being set at the start

restart <= 1’b0;

start_reg0 <= 1’b0; start_reg1 <= 1’b0;

finish_reg0 <= 1’b0; finish_reg1 <= 1’b0;

end

else

begin

start_reg0 <= start; start_reg1 <= start_reg0;

finish_reg1 <= finish_reg0;

/** Check timing unit **/

if(delay_unit)

cnt_full <= 32’d50_000*2-32’d2; // Timing for 2ms Replace N with actual value during instantiation: 32’d50_000*N-32’d2

else

cnt_full <= 32’d50*2-32’d2; // Timing for 2us

/***************/

/** Whether to restart **/

if(start_pose) // Detected start time

restart <= 1’b1;

/**** Timing completed ****/

else if(full) // Delay ends

begin

cnt <= 32’d0; // Reset cnt

finish_reg0 <= 1’b1; // Finish response

restart <= 1’b0;

end

/***************/

/**** Timing starts ****/

else if(restart)

begin

finish_reg0 <= 1’b0; // Reset finish for new delay

cnt <= cnt+1’b1;

end

/***************/

/** Wait for new timing **/

else

begin

cnt <= cnt;

finish_reg0 <= finish_reg0;

restart <= restart;

end

end

end

assign start_pose = (~start_reg1&start_reg0)?1’b1:1’b0; // Start rising edge detection

assign finish_pose = (~finish_reg1&finish_reg0)?1’b1:1’b0; // Finish rising edge detection

assign full = (cnt_full-cnt==0)?1’b1:1’b0; // Check if counted full

assign finish = finish_reg0;

endmodule

/**************************************************************************************************/ /***************************************ModelSim********************************************/

`timescale 1ns/1ps

module delay_tb();

reg clk,rst_n;

reg start;

wire finish,finish_pose;

delay delay_u0

(.clk(clk),

.rst_n(rst_n),

.start(start),

.delay_unit(1’b1),

.finish(finish),

.finish_pose(finish_pose));

//defparam delay_u0.N = 2; // Delay 2ms

initial

begin

clk = 1’b0;

rst_n = 1’b0;

start = 1’b0;

#1000 rst_n = 1’b1;

#4010 start = 1’b1; #50 start = 1’b0; end

always #10 clk = ~clk;

endmodule

Concept:

The start port triggers the delay on the rising edge, the finish port is set when the delay ends (reset after restarting the delay), and the rising edge detection of finish is already done inside the module (the finish_pose port), which can be called directly. The delay_unit port is set high to select ms, and low to select us. The #(parameter N) is the timing duration, for example, timing for 8ms: “N = 8, .delay_unit(1’b1)”. During actual instantiation, just use “defparam instantiation_name.N = value”. Since ModelSim cannot recognize this call, the actual value is used instead of N for testing. Edge detection consumes two clock cycles, so cnt_full needs to be reduced by 2, and finish_reg0 is directly connected to the finish output port instead of using finish_reg1 to connect to finish.

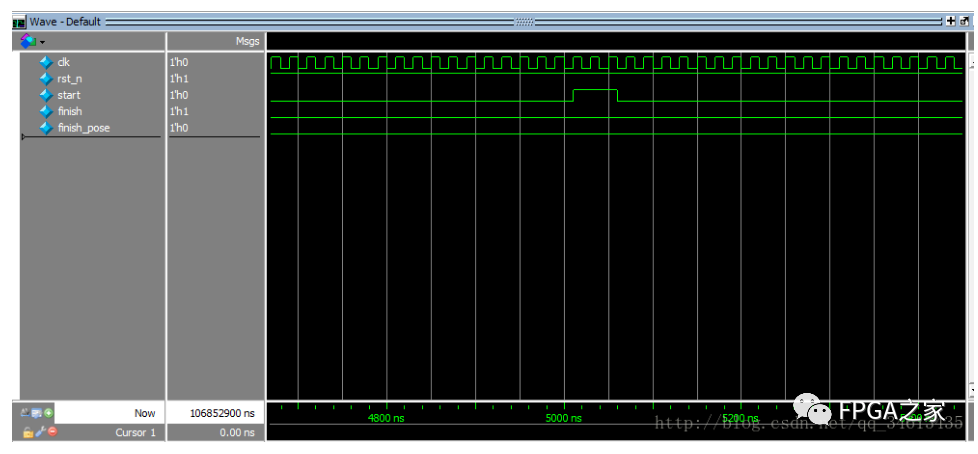

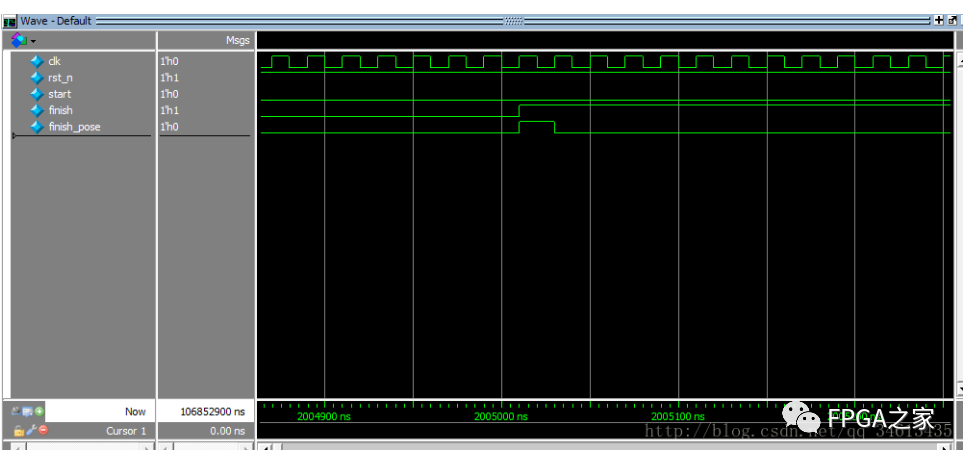

The start time (5010ns) and end time (2005010ns) for testing the delay of 2ms:

————————————————

Welcome communication engineers and FPGA engineers to follow our official account

The largest national FPGA WeChat technical group

Welcome everyone to join the national FPGA WeChat technical group, which has tens of thousands of engineers, a group of engineers who love technology, where FPGA engineers help each other, share, and have a strong technical atmosphere! Hurry up and invite your friends to join!!

Just press and hold to join the national FPGA technical group

FPGA Home Component City

Advantageous component services, please scan the code to contact the group owner: Jin Juan, Email: [email protected] Welcome to recommend to procurement

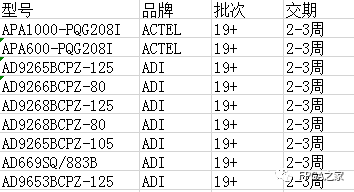

ACTEL, AD part of advantageous ordering (full series):

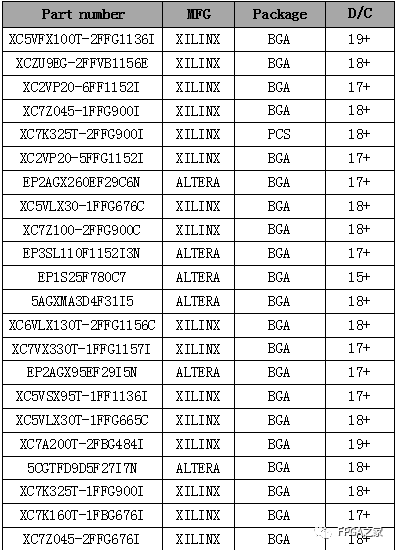

XILINX, ALTERA advantageous stock or ordering (full series):

(The above components are partial models, please consult the group owner Jin Juan for more models)

Service philosophy: FPGA Home Component City aims to facilitate engineers to quickly and conveniently purchase components. After years of dedicated service, our customer service is spread across large listed companies, military research units, and small and medium-sized enterprises. Our biggest advantage is emphasizing service first, and achieving fast delivery and favorable prices!

Directly operated brands: Xilinx, ALTERA, ADI, TI, NXP, ST, E2V, Micron, and over a hundred other component brands, especially good at dealing with components subject to embargoes from the US and Europe.We welcome engineer friends to recommend us to procurement or consult us directly!We will continue to provide the best service in the industry!

FPGA technical group official thanks to brands: Xilinx, Intel (Altera), Microsemi (Actel), Lattice, Vantis, Quicklogic, Lucent, etc.