Global ASIC Design Services Market Share, Size, and Technology Research Report 2025

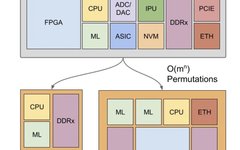

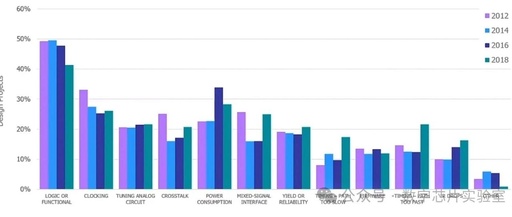

ASIC design services refer to the services for designing and optimizing Application-Specific Integrated Circuits (ASICs) for specific applications. ASIC chips are characterized by high performance, low power consumption, and high integration, and are typically used in fields with high functional requirements, such as communications, consumer electronics, automotive electronics, and industrial control. ASIC design services cover … Read more