Paper Information:

EDIMS: an event-driven internal memory synchronized readout prototype ASIC chip developed for HFRS-TPC

Yang, M., Qian, Y., Pu, T., Lu, W., Sun, Z., Zhao, H., Zhang, J., & Liu, Z.

DOI:10.1007/s41365-023-01341-w

Article Highlights

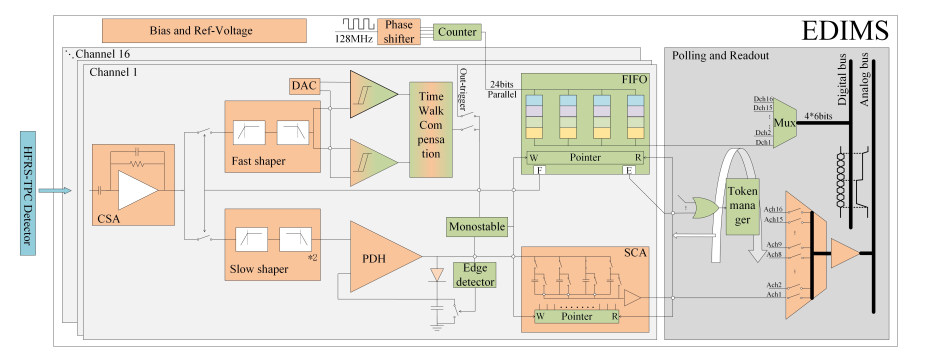

HFRS is a radioactive secondary beam separator at China’s high-current heavy ion accelerator facility HIAF. Several high-count-rate TPC detectors are planned for particle identification and beam monitoring. This article proposes an event-driven front-end readout ASIC chip with internal storage and synchronized readout—EDIMS. This chip features high count rates and a large dynamic range, enabling high-precision time and charge measurements of the TPC detector output signals. Based on a 0.18 μm CMOS process and a mixed analog-digital design approach, the first 16-channel prototype EDIMS chip was developed. Each channel consists of a charge-sensitive front-end, fast and slow shaping circuits, peak detection and holding circuits, a discriminator with time drift compensation, an analog memory, and a FIFO. The chip’s top-level multiplexing module includes a token ring manager, an analog bus and digital bus, clock phase-shifting circuits, and time interval measurement modules. Currently, the chip has completed tape-out and testing. Tests indicate that EDIMS has good time and amplitude resolution, essentially meeting the application requirements of HFRS-TPC.

Chip Structure Block Diagram

https://doi.org/10.1007/s41365-023-01341-w