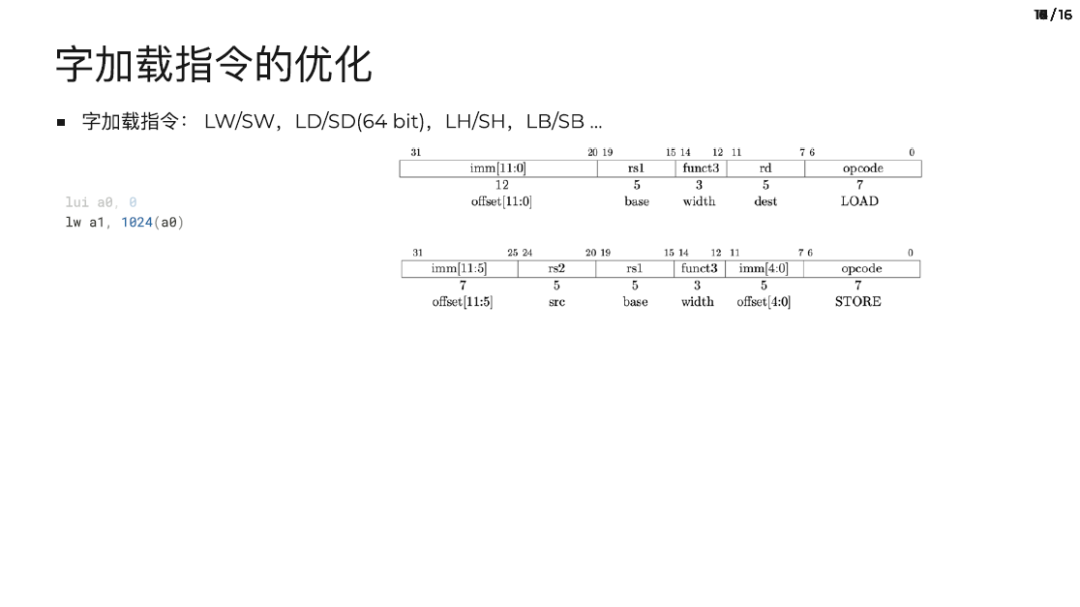

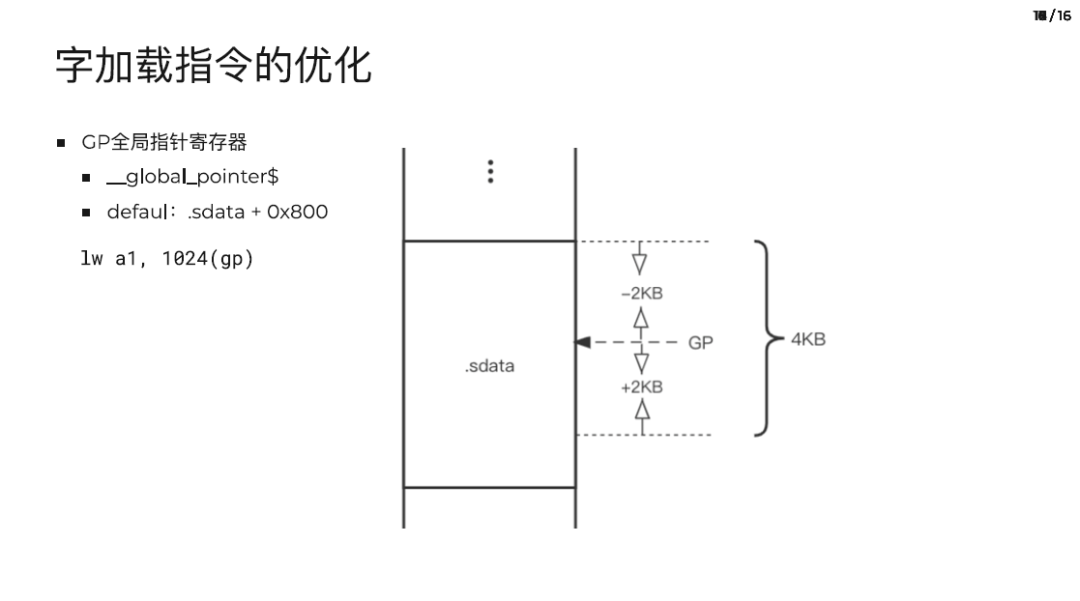

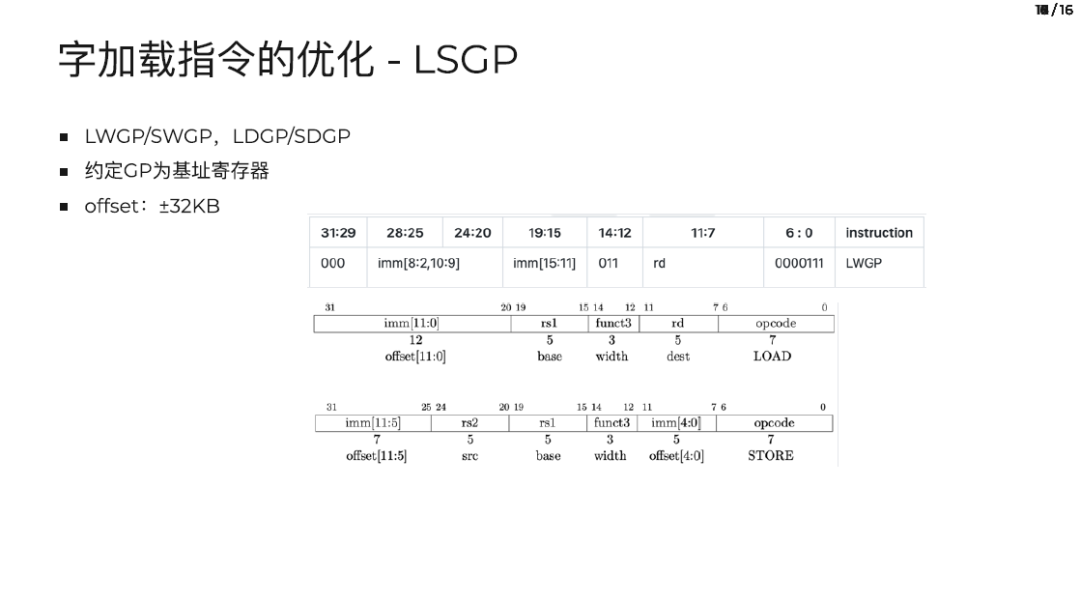

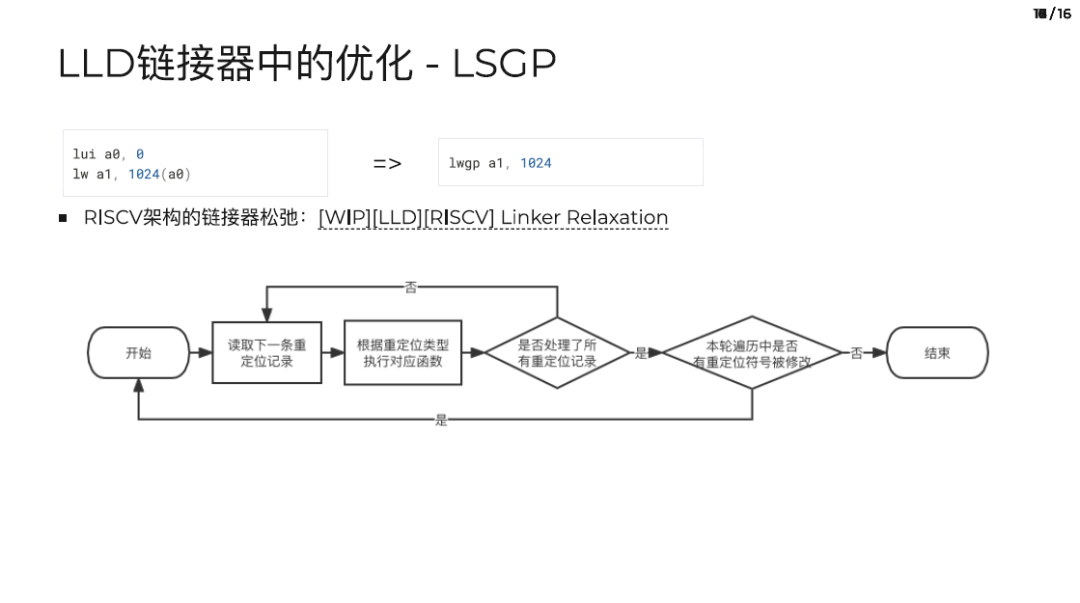

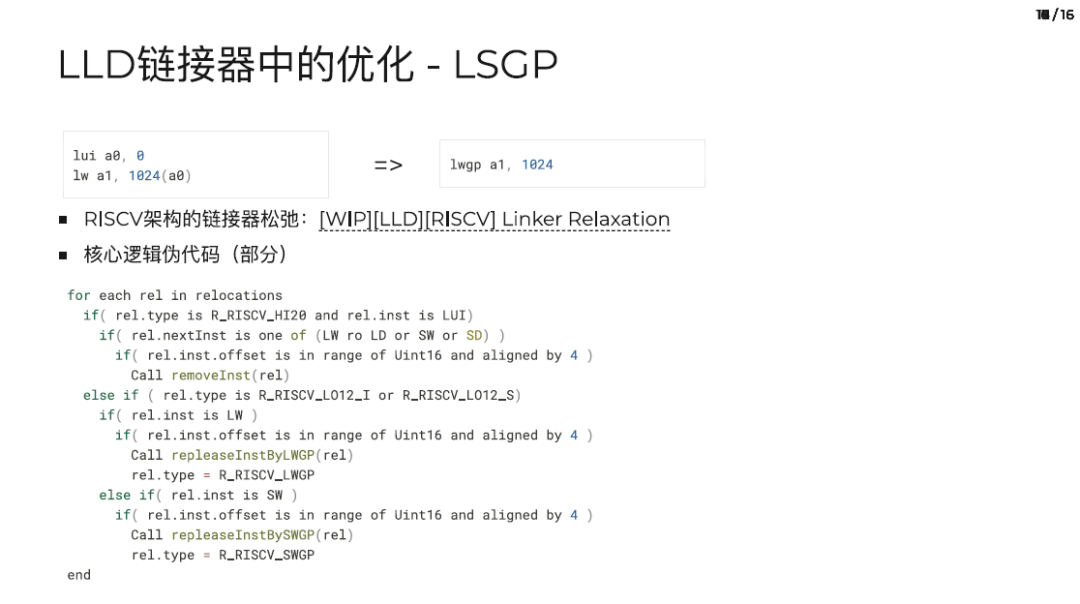

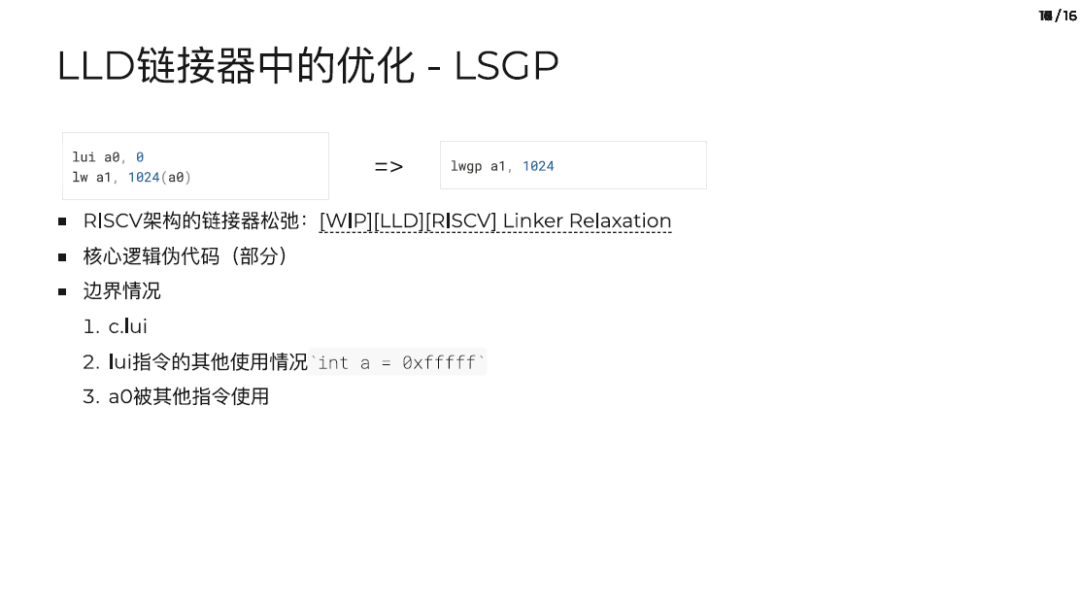

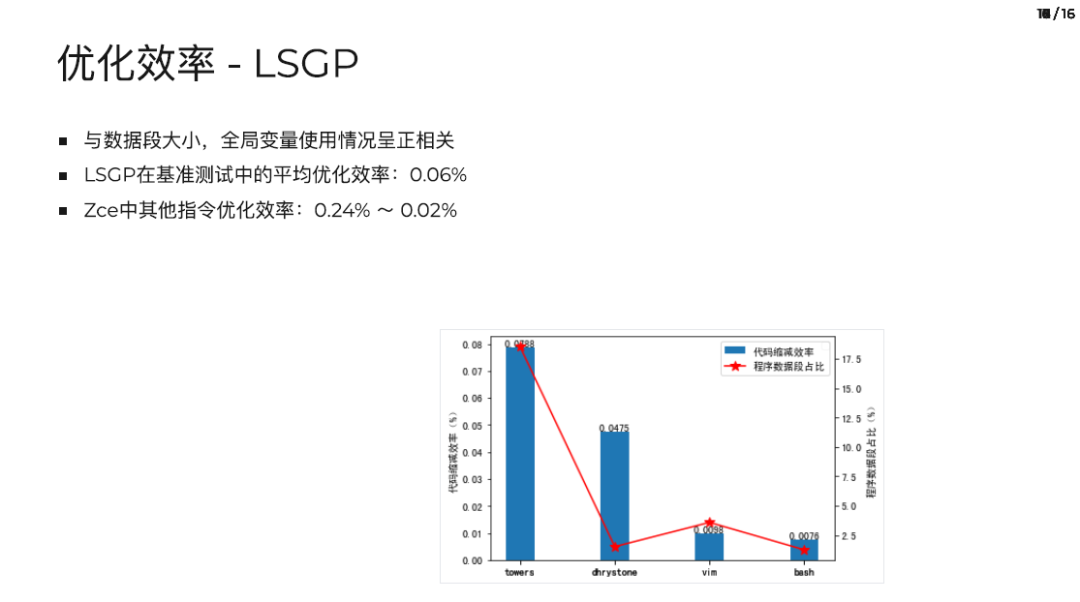

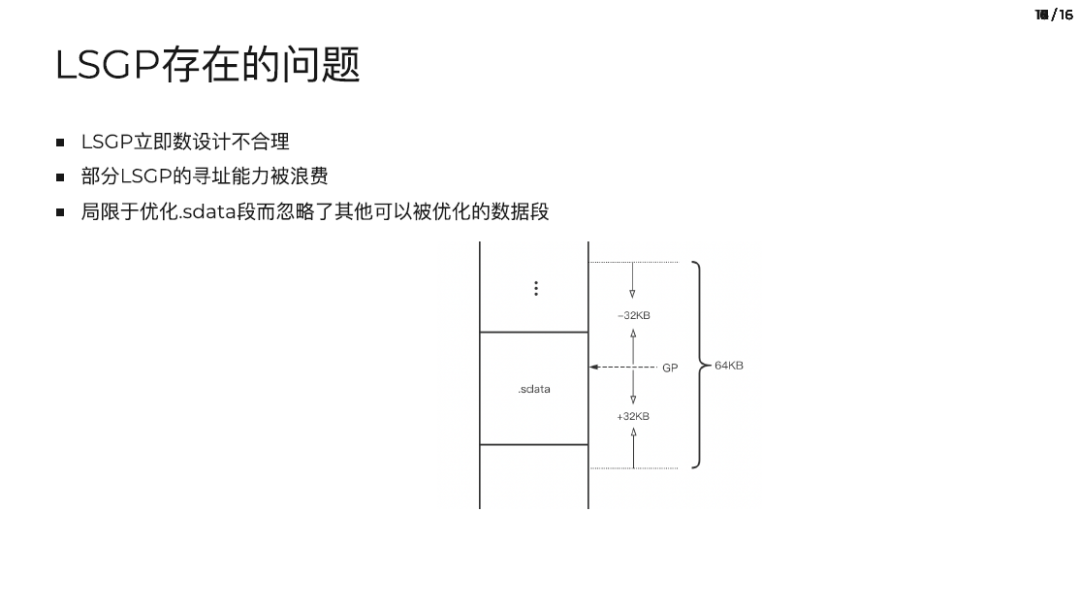

RISC-V, as a representative of reduced instruction set computing, also reflects some of the drawbacks of reduced instruction sets, one of which is the larger program size. In reduced instruction set computing (RISC), the number of instructions required to implement some complex operations is generally greater than that of complex instruction set computing (CISC), leading to a larger final binary program size compared to CISC programs. Moreover, embedded devices typically have limited RAM and ROM, making program size especially important in embedded scenarios. To optimize the program code size of RISC-V as much as possible based on the existing compressed instruction set, a series of instructions were established in the RISC-V instruction set sub-extension Zce. Among them, a series of instructions represented by LWGP are used to reduce the number of instructions when loading/storing byte data. This paper analyzes the optimization principles of instructions represented by LWGP on code size and implements them in the LLD linker. By analyzing the changes in program size before and after using instructions like LWGP, the efficiency of binary program size optimization is evaluated, and subsequent improvement suggestions are proposed.

Scan the QR code to read the full article