In the past year or two, the open-source instruction set architecture RISC-V has received unprecedented support from the industry due to its advantages such as open-source, free, modular, and scalable. Major companies including Qualcomm, Google, NVIDIA, Samsung, Western Digital, SiFive, PingTouGe, ChipLink, XuanYuan Microelectronics, GigaDevice, and hundreds of others are vigorously supporting the RISC-V ecosystem, promoting a tripartite division of power among the RISC-V, X86, and ARM architectures.

According to market research firm Semico Research, the number of chips using the RISC-V architecture is expected to reach 62.4 billion by 2025, with a compound annual growth rate of 146% from 2018 to 2025.

The RISC-V instruction set is completely open-source, designed simply, easy to port Unix systems, and features modular design with a complete toolchain. It has a wealth of open-source implementations and tape-out cases. Although it is not the first open-source instruction set (ISA), it is the first instruction set architecture designed to allow the selection of a suitable instruction set according to specific scenarios. Based on the RISC-V instruction set architecture, CPUs for server, home appliances, industrial control, and sensors can be designed. The industry believes that RISC-V will achieve great success in the smart IoT field!

Academician Ni Guangnan from the Chinese Academy of Engineering believes that in the future development of chips, chip architecture should not be subject to external constraints. Developing RISC-V open-source chip architecture is an opportunity, as RISC-V is completely open-source and free, making it very suitable for China’s massive market demand. China has the largest number of chip design companies in the world, and the number of CPU applications in China is also the largest globally.

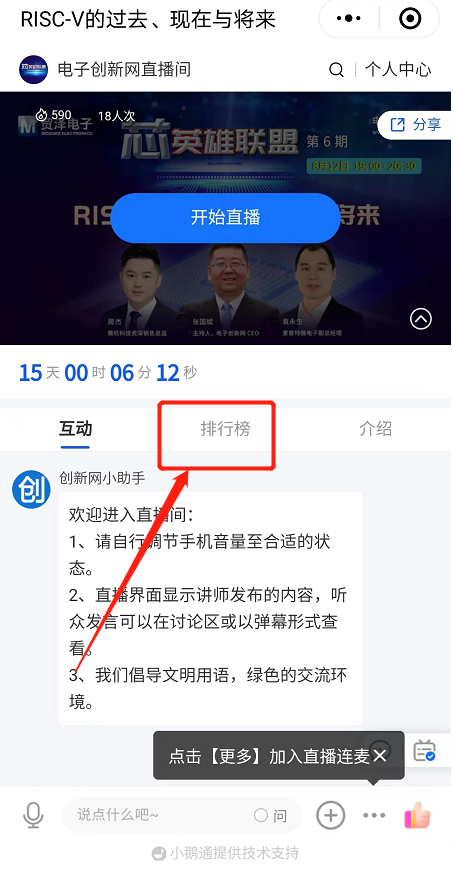

To better promote the local RISC-V ecosystem, on August 9th at 19:00, the “Mouser Electronics Chip Hero Alliance Live” program invited two experts from local RISC-V leading companies, SiFive and Aptina Microelectronics, to discuss the past, present, and future of RISC-V. The two experts will also share the latest product information based on the RISC-V architecture. Everyone is welcome to reserve for the live broadcast!

Guest Introduction

Guest Speaker 1: Zhou Jie

Senior Sales Director at SiFive and founding member. Master’s degree in Physical Electronics from the University of Science and Technology of China, with 13 years of experience in semiconductor industry IP and chip development, closely related to RISC-V for nearly 5 years, possessing a deep understanding of the development status and overall ecosystem of RISC-V.

Guest Speaker 2: Yuan Yongsheng

Deputy General Manager of Aptina Microelectronics.

Host: Zhang Guobin

Founder and CEO of Electronic Innovation Network, graduated from Xi’an University of Electronic Science and Technology with a major in Electronic Engineering, a well-known KOL in the semiconductor field. He has many years of experience in semiconductor media content and operations, having written numerous industry analysis articles. (WeChat ID: 18676786761)

Inviting Influencers List

During this live broadcast, we will also launch an Inviting Influencers List activity. As long as you forward your exclusive invitation posterto 6 related semiconductor WeChat groups and screenshot it for the editor (WeChat ID: eetrend89), attracting more people to sign up, you will have a chance to win a JD gift card. Hurry up and participate! (Note: After successfully scanning the reservation, click the ranking button to get your personal exclusive poster. Long press the poster to save it, and then post it in 6 related semiconductor WeChat groups, etc.)

Participating in the Inviting Influencers List activity only requires three simple steps:

Step 1: Click on the Ranking

Step 2: Click on the Ranking Button

Step 3: Generate an Exclusive Poster, Publish it to Moments or WeChat Groups

Important Notice

For malicious ranking manipulators, they will have their ranking qualifications canceled and be prohibited from participating in all future Chip Hero Alliance live broadcasts. The final interpretation of this reward belongs to the Electronic Innovation Network.

About the “Chip Hero Alliance” Live Broadcast