The architecture of RD-V2 supports the design of computing subsystems for infrastructure segments such as hyperscale data centers, networking, and enterprise storage.

3.1 IP in RD-V2

The IP and components in RD-V2 provide a design foundation for creating custom System-on-Chips (SoCs).

The RD-V2 subsystem includes the following IP:

• Armv9.0-A Arm Neoverse V2 core

• Arm Neoverse CMN-700 coherence mesh network

• Arm Cortex-M7 system control processor

• Arm Cortex-M7 manageability control processor

• Arm CoreLink GIC-700 generic interrupt controller

• Arm CoreLink MMU-700 system memory management unit

• Arm CoreLink PCK-600 power control kit

• Arm CoreLink NI-700 on-chip network interconnect

• Arm CoreLink NIC-450 network interconnect

• Arm® CoreLink™ ADB-400 AMBA® domain bridge

• Arm CoreSight on-chip system SoC-600

• Arm CoreSight STM-500 system trace macrocell

• Clock generator supporting dynamic clock gating

• On-chip ROM, RAM, and other peripherals

• Third-party DDR5 – 5600 memory controller

3.2 System Architecture

RD-V2 is divided into multiple functional modules, which are a combination of the main IP and their surrounding support logic. Some functions of this design integrate the capabilities of multiple modules. This modular design approach provides flexibility, scalability, and modularity.

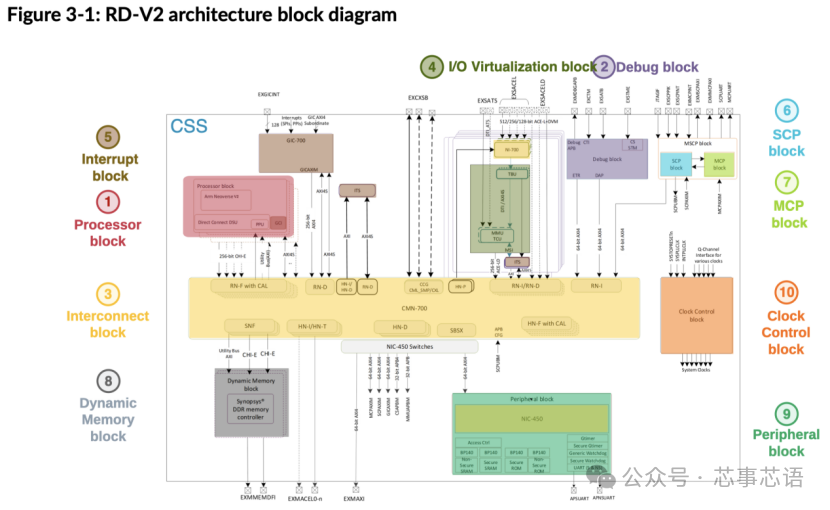

The following diagram illustrates the top-level architecture of RD-V2.

The functional modules in RD-V2 are as follows:

·Interconnect Module: Includes both coherent and non-coherent interconnects.

·CMN-700 is a coherent interconnect based on a mesh architecture, supporting multi-chip connections via Coherent Mesh Link SMP (CML_SMP) or CXL 2.0.

·NI-700 connects to external I/O controllers and provides an extended interface for CMN-700.

·NIC-450 interfaces with system peripherals, the remaining components of the System-on-Chip (SoC), and other subsystems.

·Also includes lower-performance interconnects such as AMBA AXI4-Stream interconnect (IC) and Advanced Peripheral Bus (APB) IC.

·For more information, see the “Interconnect Module”.

·Figure 3-1: RD-V2 Architecture Block Diagram

·Processor Module: Contains the Arm Neoverse V2 core with Direct connect DynamIQ shared unit (DSU) and power management components.

·Each cluster (MP1) configures one core plus a bridge.

·RD-V2 implements 32 instances of the processor module.

·For more information, see the “Processor Module”.

·Interrupt Module: Handles interrupts in the system.

·Includes distributed GIC-700 components, such as GIC distributor and redistributor, as well as Interrupt Translation Service (ITS).

·For more information, see the “Interrupt Module”.

·I/O Virtualization Module: Includes distributed Translation Buffer Unit (TBU) and Translation Control Unit (TCU) components, providing I/O virtualization capabilities for external I/O controllers.

·For more information, see the “I/O Virtualization Module”.

·Debug Module: Supports CoreSight debugging and tracing for all cores, mesh networks, and other system IP in the computing subsystem.

·For more information, see the “Debug Module (Debug and Trace)”.

·MSCP Module: Includes a system control processor based on Cortex-M7 and a manageability control processor.

·The System Control Processor (SCP) controls functions such as boot, reset, clock, and power management.

·The Manageability Control Processor (MCP) handles communication with the Baseboard Management Controller (BMC). Supports MHUv2.1 inter-processor communication methods.

·Includes a PCK-600 power control kit distributed across the subsystem to support different reset and power domains.

·Provides extended interfaces for adding SoC peripherals (such as Shared Peripheral Interrupt (SPI) and I2C).

·For more information, see the “MSCP Module”.

·Clock Control Module: Contains logic for generating clocks for the computing subsystem.

·Uses separate clock control logic to generate clocks for each core, debug logic, and memory controller.

·For more information, see the “Clock Control Module”.

·Peripheral Module: Includes watchdog timers, secure and non-secure general-purpose timers, and secure and non-secure general-purpose asynchronous transceivers (UART).

·Also includes scratch RAM, boot ROM, and firmware ROM.

·For more information, see the “Peripheral Module”.

·Dynamic Memory Module: Contains third-party memory controllers.

·For more information, see the “Dynamic Memory Module”.