01

—

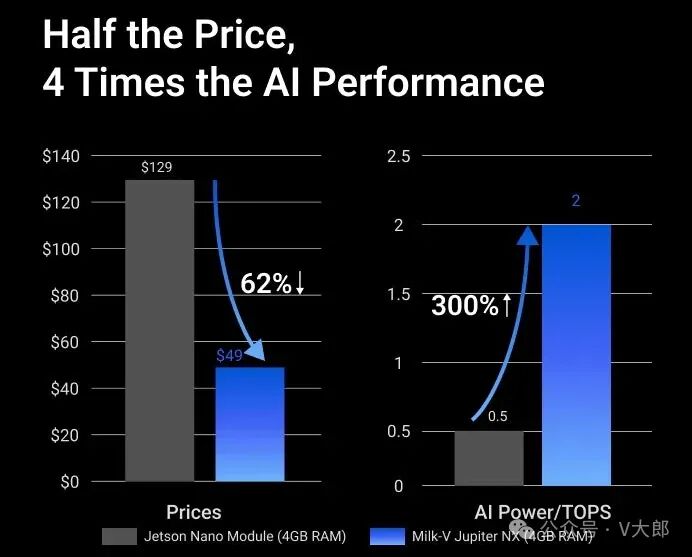

New Member of the K1/M1 Family: Jupiter NXJupiter NX is a system on module (SoM) launched by Shenzhen Milk-V Technology, featuring the SpacemiT K1/M1 octa-core 64-bit RISC-V processor, designed as an alternative to NVIDIA Jetson Nano/NX.This module is compatible with the 260-pin SO-DIMM interface of Jetson Nano/Xavier NX, allowing it to work with existing carrier boards. Specifications

Specifications

-

Processor:SpacemiT K1/M1, 8-core X60 RISC-V (RV64GCVB) @ 1.6 GHz

-

Graphics Processor:Imagination IMG BXE-2-32 @ 819 MHz, supporting OpenGL ES 3.2, Vulkan 1.3, OpenCL 3.0, with a performance of 20 GFLOPS

-

Video Processor:

-

Decoding: H.265, H.264, VP8, VP9, MPEG4, MPEG2, supporting up to 4K @ 60fps

-

AI Performance: Achieving 2.0 TOPS (INT8) through “CPU core fusion”

-

Instruction Set Support:RVA 22 Profile, compatible with RVV 1.0

The Jiachen Project (RISC-V Prosperity 2036) is a public collaborative project initiated by the Chinese open-source community aimed at promoting the development of the RISC-V ecosystem, named after the traditional Chinese sexagenary cycle year of “Jiachen” (2024), symbolizing the start of a new era with “Jia” leading the way to promote the prosperous development of open-source hardware, covering the following themes: Original link: https://www.cnx-software.com/2025/05/13/jupiter-nx-som-an-nvidia-jetson-nano-nx-alternative-powered-by-spacemit-k1-octa-core-risc-v-soc/

Original link: https://www.cnx-software.com/2025/05/13/jupiter-nx-som-an-nvidia-jetson-nano-nx-alternative-powered-by-spacemit-k1-octa-core-risc-v-soc/

02

—

Paper Guide| Hardware vs. Software Implementation of Warp-Level Features in Vortex RISC-V GPU

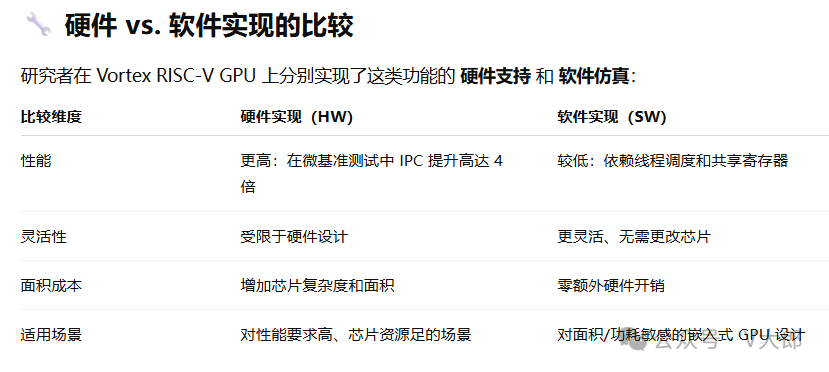

The paper studies how to implement warp-level GPU features in the open-source Vortex RISC-V GPU and compares the performance and cost differences between hardware implementation and software simulation.

Traditional GPUs are based on the SPMD (Single Program Multiple Data) model, but modern GPU programming increasingly relies on warp-level operations, such as:

-

Thread Synchronization (Synchronization Barriers)

-

Voting (Ballot)

-

Inter-thread Data Exchange (Shuffle)

These features are crucial for improving the efficiency of compute-intensive GPU applications.

Conclusion and Insights

-

If the design goal is a high-performance general-purpose GPU, it is recommended to support warp-level features through hardware methods.

-

If the goal is an embedded, small RISC-V GPU, software simulation is a cost-effective alternative.

Paper link: https://arxiv.org/abs/2505.03102

Article link: https://semiengineering.com/comparisons-of-hw-versus-sw-implementation-of-warp-level-features-in-vortex-risc-v-gpu-georgia-tech-iit/

03

RISC-V Small AI Computer ALPHA-One

Pine64 recently released its latest fanless RISC-V small computer ALPHA-One, designed for edge AI inference and local large language model (LLM) applications.The device is based on the StarPro64 single-board computer, integrating a powerful AI accelerator and rich interfaces, suitable for developers, AI enthusiasts, and the open-source hardware community.

Parameter Specifications

-

Processor:ESWin EIC7700X, equipped with 4-core SiFive P550 RISC-V CPU, clocked at 1.8 GHz.

-

Graphics Processor:Imagination AXM-8-256 GPU.

-

Neural Network Processor (NPU):Supports up to 20 TOPS (INT8) AI performance.

-

Memory:32GB LPDDR5.

-

Storage:64GB eMMC (pre-installed with Deepseek/Owen 7B LLM), additionally equipped with 128Mb SPI boot flash.

AI and LLM Support

ALPHA-One comes pre-installed with the Deepseek/Owen 7B model, supporting an inference speed of approximately 3.5 tokens/second.Pine64 indicates plans to provide support for the Meta Llama series of LLMs in the future.

Original link: https://liliputing.com/pine64-alpha-one-is-a-fanless-risc-v-mini-pc-with-up-to-20-tops-of-ai-performance/04

New CEO of RISC-V International:Andrea Gallo

RISC-V International announced on May 13, 2025, the appointment of Andrea Gallo as the new Chief Executive Officer (CEO), effective immediately.Gallo has served as the organization’s Vice President of Technology since June 2024, actively promoting the global adoption of the RISC-V instruction set architecture (ISA) and strengthening technical collaboration with global members.

Andrea Gallo’s acceptance speech: “I look forward to further advancing the technical development of RISC-V International in my role as CEO and accelerating the adoption of RISC-V in the global market. One of my top priorities is to improve the developer experience, enabling companies to innovate faster and focus on their differentiation.”

RISC-V Development Trends

After taking office as CEO, Gallo proposed the following development directions:

-

Enhancing Developer Experience: By expanding technical and educational resources to help companies accelerate innovation.

-

Promoting Technical Standardization: Accelerating the formulation and certification of RISC-V extensions and specifications to enhance technical trust.

-

Expanding the Ecosystem: Collaborating with the RISE project to improve compiler, toolchain, system library, kernel, virtualization, programming language, Linux distribution integration, as well as debugging, analysis, and AI/ML tool software resources.

-

Increasing Accessibility of Development Boards: Making it easier for global developers to access RISC-V development boards, promoting technology dissemination.

Original link: https://www.design-reuse.com/news/202528673-risc-v-international-promotes-andrea-gallo-to-ceo/

05

e-GPU : Open-source RISC-V GPU Platform for TinyAI Devices

Researchers at EPFL (École Polytechnique Fédérale de Lausanne) recently released a technical paper titled “e-GPU,” introducing an open-source, configurable RISC-V graphics processing unit (GPU) platform aimed at TinyAI devices.Traditional GPUs excel in parallel processing but have not been widely adopted in ultra-low-power edge devices (TinyAI) due to power and area constraints, as well as a lack of suitable programming frameworks. To address these challenges, researchers proposed the e-GPU platform, which features:

-

Open-source and Configurability: e-GPU is an open-source platform that allows configuration according to specific needs to optimize area and power consumption, meeting the constraints of TinyAI devices.

-

Lightweight Programming Framework: Introduced Tiny-OpenCL, a lightweight programming framework designed for resource-constrained environments, simplifying the complexity of using GPUs on TinyAI devices.

-

Integration with X-HEEP Platform: e-GPU is integrated into the scalable heterogeneous energy-efficient platform (X-HEEP), forming an Accelerated Processing Unit (APU) to validate its adaptability in practical applications.

This research provides new ideas and solutions for integrating GPUs into ultra-low-power edge devices, promoting further development of TinyAI devices in terms of performance and energy efficiency.

Paper link: https://arxiv.org/abs/2505.08421Original link: https://semiengineering.com/embedded-gpu-an-open-source-and-configurable-risc-v-gpu-platform-for-tinyai-devices-epfl/06

OpenLibm: A Cross-Platform Mathematical Library

OpenLibm is a high-quality, portable, standalone C mathematical library (libm) designed to provide consistent and reliable mathematical function support for applications and programming language implementations.OpenLibm can be used as a standalone library or integrated into other projects.Its build process is straightforward, suitable for developers needing custom mathematical function implementations. OpenLibm supports multiple operating systems, including Linux, macOS, Windows, FreeBSD, OpenBSD, NetBSD, and DragonFly BSD.It can be built using GCC and Clang compilers and supports various architectures such as x86, amd64, arm, aarch64, riscv64, ppc64le, mips, wasm32, s390(x), and loongarch64.Original link: https://blog.adafruit.com/2025/05/14/openlibm-a-high-quality-portable-standalone-c-mathematical-library/

OpenLibm supports multiple operating systems, including Linux, macOS, Windows, FreeBSD, OpenBSD, NetBSD, and DragonFly BSD.It can be built using GCC and Clang compilers and supports various architectures such as x86, amd64, arm, aarch64, riscv64, ppc64le, mips, wasm32, s390(x), and loongarch64.Original link: https://blog.adafruit.com/2025/05/14/openlibm-a-high-quality-portable-standalone-c-mathematical-library/