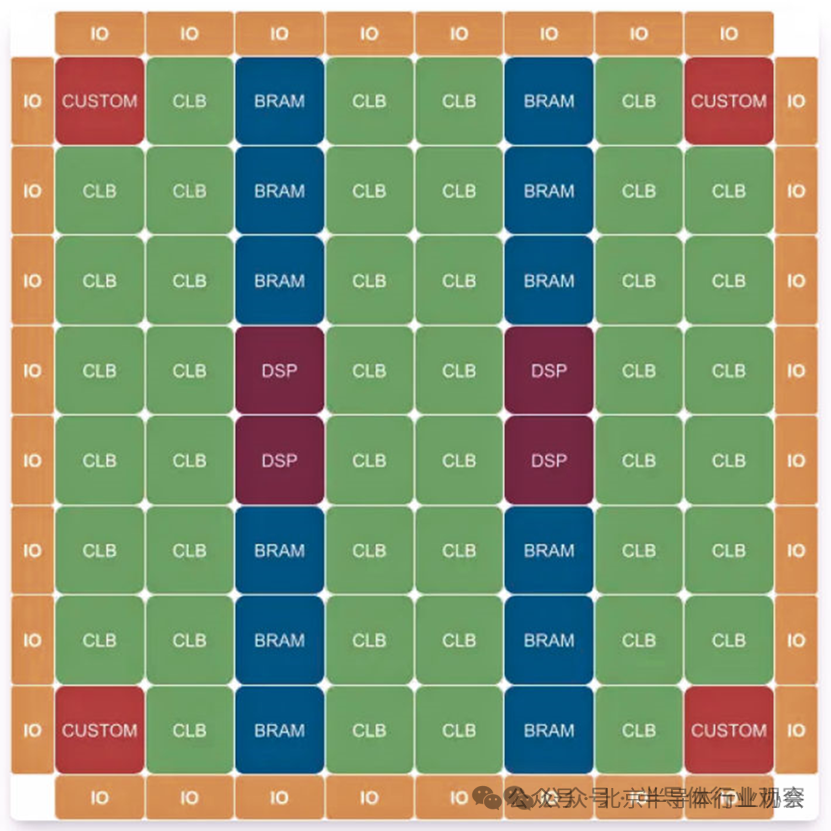

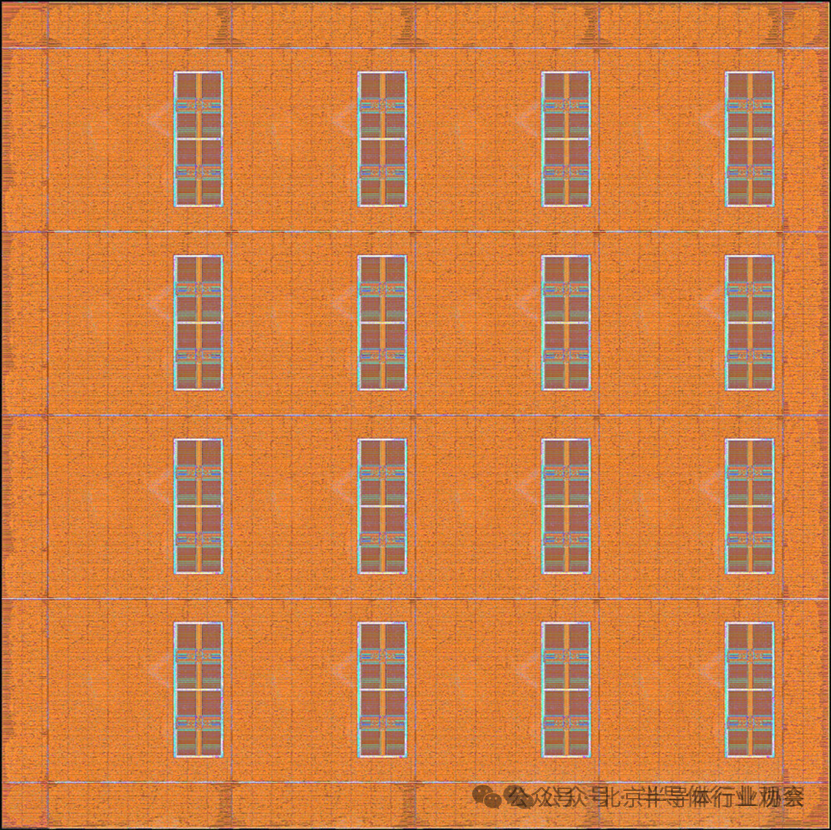

(Source: eejournal)Previously, we reported on an open-source FPGA company, which can be referenced in the article “The World’s First Open Source FPGA Officially Released.” Recently, eejournal interviewed the CEO of this company to discuss the opportunities in the highly competitive FPGA market.The following is the main text of the article:Embedded FPGA (eFPGA) IP is not a new concept. Several companies, including Achronix, Efinix, Flex Logix, Menta, and QuickLogic, have long provided FPGA cores that can be integrated into ASICs and SoCs. ASIC designers use eFPGA cores to ensure their designs are future-proof. eFPGA can be used to patch errors or add features as needed. These capabilities help avoid the costly and time-consuming redesigns associated with ASICs. eFPGA is a challenging IP business with a limited market, primarily utilized by semiconductor developers in the defense and aerospace sectors.In November last year, ADI acquired all technical assets of Flex Logix and hired its technical team, effectively sidelining one of the most prominent players in the field—Flex Logix founder and CEO Geoff Tate. Currently, it seems that ADI will only use the acquired eFPGA IP internally.However, there is now a new player in the eFPGA IP space—Zero ASIC, which is already a mature IP provider. Zero ASIC’s eFPGA IP product is named Platypus. The company’s new eFPGA products (including IP cores, FPGA bitstreams, and tools) are all offered under open standards.Typically, I would write some text to describe this situation. However, I will directly quote Zero ASIC’s Platypus press release, as the summary by the company’s CEO Andreas Olofsson is excellent:For FPGA-based systems in aerospace, defense, healthcare, communications, automotive, and industrial applications, obsolescence is a critical issue, as these systems often have lifespans of 10 to 50 years. For example, take the F-35 fighter jet, which began development in 1997 but only entered full production in 2021. During this time, transistor density increased by 10,000 times, and the FPGA industry has introduced six generations of new architectures.“The mismatch between the continuous advancement of semiconductor technology and the slow infrastructure development cycles has led the U.S. military to spend approximately $50 billion to $70 billion on non-engineering costs associated with device obsolescence, with 15% of all replacement semiconductor parts being counterfeit.”These two paragraphs outline the basic principles of eFPGA IP, which can help ASIC or SoC designs become more resilient by adding a certain degree of programmability. However, the effectiveness of this programmability within the chip entirely depends on the placement of the eFPGA module within the chip architecture.The press release continues:Since the advent of FPGAs in the 1980s, commercial FPGA products have become increasingly complex, less standardized, and less transparent, exacerbating issues related to device obsolescence and counterfeiting. At best, a discontinuation notice for an FPGA device or eFPGA IP core can lead to a complete redesign of an entire subsystem. At worst, it can result in the termination of an entire program.This paragraph covers two major complaints against established FPGA chip suppliers. First, they focus on manufacturing increasingly complex FPGAs that are harder to use than previous devices. This is true across the semiconductor industry and not unique to the FPGA field. Secondly, discontinuation notices are a headache in any field. Similarly, this is the survival path of the chip industry. What is not mentioned in this paragraph is that FPGA manufacturers are typically good at maintaining production of older products for decades, so the issue of FPGA obsolescence is mainly limited to long-lived designs, such as those found in defense and aerospace projects like the F-35 fighter jet mentioned in Zero ASIC’s press release. The press release continues:“A reasonable next step to address FPGA obsolescence and counterfeiting issues is to move away from single-source components and establish a set of open-standard FPGA architectures, similar to the successful standards created for memory and passive components.”This statement shows a significant leap of confidence from problem statement to solution. This is precisely the premise behind Zero ASIC’s creation of the Platypus eFPGA IP and its related tools. Next, let’s take a closer look at the products just released by Zero ASIC and interview Olofsson.As shown in the Platypus block diagram below, Zero ASIC’s eFPGA looks very similar to any tiled FPGA, containing blocks such as logic, block RAM (BRAM), DSP, and I/O. Custom blocks can also be included within the FPGA array. This is the advantage of eFPGA, differing from standard FPGA chips. Currently, the Platypus eFPGA array offered by Zero ASIC consists solely of CLB Tiles, containing a total of 2048 LUTs and 1024 I/O Tiles. The company is developing larger Platypus eFPGA arrays, with the number of LUTs reaching up to 131,072 and I/O Tiles up to 8048. These planned eFPGA arrays are suitable for medium to small FPGA chips, but the advantage of eFPGA lies in its ability to connect to the internal workings of ASICs or SoCs through thousands of on-chip connections, ensuring faster data transfer speeds within the system.So far, the company has developed an eFPGA array, the experimental Z1010 heterogeneous eFPGA, which includes LUTs, DSP, and BRAM, and has been ported to GlobalFoundries’ GF12LP manufacturing process. The following image shows the experimental Z1010 array. According to the company, “The official Z1010 standard eFPGA array will contain varying proportions of LUTs, DSP, and BRAM.”

Currently, the Platypus eFPGA array offered by Zero ASIC consists solely of CLB Tiles, containing a total of 2048 LUTs and 1024 I/O Tiles. The company is developing larger Platypus eFPGA arrays, with the number of LUTs reaching up to 131,072 and I/O Tiles up to 8048. These planned eFPGA arrays are suitable for medium to small FPGA chips, but the advantage of eFPGA lies in its ability to connect to the internal workings of ASICs or SoCs through thousands of on-chip connections, ensuring faster data transfer speeds within the system.So far, the company has developed an eFPGA array, the experimental Z1010 heterogeneous eFPGA, which includes LUTs, DSP, and BRAM, and has been ported to GlobalFoundries’ GF12LP manufacturing process. The following image shows the experimental Z1010 array. According to the company, “The official Z1010 standard eFPGA array will contain varying proportions of LUTs, DSP, and BRAM.” There is little detailed description on Zero ASIC’s website regarding the various Platypus Tiles. It seems that the number of LUTs per CLB, the number of inputs per LUT, and the number of routing channels between Tiles can be independently configured, which may lead to interesting optimizations that some FPGA chips cannot achieve. Zero ASIC’s website does not describe the capacity of the BRAM Tiles or the composition of the DSP Tiles, so if you want to know these details, you need to contact the company directly.Zero ASIC’s eFPGA product also includes a tool called FPGA Architect, which is an EDA platform that generates the correct embedded FPGA core. FPGA Architect can automatically generate the following: Verilog RTL and netlistsEnhanced array layout macros (DEF/GDS)The architecture files for the company’s Logik EDA toolsTesting and integration infrastructureBased on information from Zero ASIC’s press release, I asked Olofsson some questions about the product. Here are my questions and his answers:Steve Leibson: “The first question is about the tools. Is Logik a product of Zero ASIC? Or is it someone else’s product? I think tools are as important as cores, so this is an important question for me.”Andreas Olofsson: “Logik is a free open-source FPGA toolchain developed by Zero ASIC. Essentially, it is a free product, similar to GCC, Linux, Pytorch, LLVM, etc. You can find all the source code here: https://github.com/siliconcompiler/logik.”Logik relies on many mature open-source components developed over the years. Overall, the time and materials invested by some very smart people in these open-source tools may exceed $20 million.High-level synthesis (Bambu/Panda (Politecnico di Milano), over 10 years)Logic synthesis (Yosys/ABC (Berkeley), over 10 years)Place and route (VPR (Toronto), 25 years) IP Package management (SiliconCompiler, 4 years)“VPR and ABC are the cornerstones of several commercial toolchains, but vendors have not publicly disclosed them.”Steve Leibson: “I think you already know that other FPGA IP suppliers like Flex Logix and Menta have not achieved such impressive results. Jeff Tate, after selling his FPGA IP company (Flex Logix), is now ‘self-employed’ on LinkedIn. I am interested in why Zero ASIC believes its FPGA IP products will be different. It’s a bit like Bullwinkle saying in ‘The Rocky and Bullwinkle Show’, ‘This time it’s for sure!’, or Charlie Brown kicking the football held by Lucy van Pelt again, only to have it fly away as usual, landing on his back.”Andreas Olofsson: “The eFPGA IP market is a niche market, so it’s not easy. IP is hard to do, and only a few vendors do it well. As a subset of this market, the eFPGA market has a high sales threshold, making it nearly impossible to grow.”That said, Zero ASIC is the first company to attempt an open architecture approach. We license our hard IP cores but allow anyone who wants to clone the architecture/bitstream (including our customers) to do so for free. This means customers will never be trapped in an architecture obsolescence situation (for example, if the company is sold or goes out of business).We will not compete with Xilinx/Altera in terms of original lookup tables (LUTs) or the richness of toolchain/IP features in the short term. Our success depends on several factors:Customers must appreciate our open philosophy. If they value PPA (power, performance, and area) over openness, then we still have room for improvement compared to competitors. eFPGA The market itself (how many customers can do something useful with 2K to 100K LUT cores?)Customers accepting our Python-based toolchain (no GUI, no TCL) and finding it “good enough.”I hope we can agree that RISC-V has made a significant change in the CPU space. The success of RISC-V stems from the market’s desire for openness. Whether FPGAs can achieve the same success remains to be seen.“Final note: Ultimately, our open eFPGA cores will also be offered in standardized chip forms (2mm x 2mm, 4.1mm x 4.1mm).”That’s all the details about Zero ASIC’s eFPGA products. Perhaps it is exactly what you need for your next ASIC or SoC design. Andreas Olofsson firmly believes it is.

There is little detailed description on Zero ASIC’s website regarding the various Platypus Tiles. It seems that the number of LUTs per CLB, the number of inputs per LUT, and the number of routing channels between Tiles can be independently configured, which may lead to interesting optimizations that some FPGA chips cannot achieve. Zero ASIC’s website does not describe the capacity of the BRAM Tiles or the composition of the DSP Tiles, so if you want to know these details, you need to contact the company directly.Zero ASIC’s eFPGA product also includes a tool called FPGA Architect, which is an EDA platform that generates the correct embedded FPGA core. FPGA Architect can automatically generate the following: Verilog RTL and netlistsEnhanced array layout macros (DEF/GDS)The architecture files for the company’s Logik EDA toolsTesting and integration infrastructureBased on information from Zero ASIC’s press release, I asked Olofsson some questions about the product. Here are my questions and his answers:Steve Leibson: “The first question is about the tools. Is Logik a product of Zero ASIC? Or is it someone else’s product? I think tools are as important as cores, so this is an important question for me.”Andreas Olofsson: “Logik is a free open-source FPGA toolchain developed by Zero ASIC. Essentially, it is a free product, similar to GCC, Linux, Pytorch, LLVM, etc. You can find all the source code here: https://github.com/siliconcompiler/logik.”Logik relies on many mature open-source components developed over the years. Overall, the time and materials invested by some very smart people in these open-source tools may exceed $20 million.High-level synthesis (Bambu/Panda (Politecnico di Milano), over 10 years)Logic synthesis (Yosys/ABC (Berkeley), over 10 years)Place and route (VPR (Toronto), 25 years) IP Package management (SiliconCompiler, 4 years)“VPR and ABC are the cornerstones of several commercial toolchains, but vendors have not publicly disclosed them.”Steve Leibson: “I think you already know that other FPGA IP suppliers like Flex Logix and Menta have not achieved such impressive results. Jeff Tate, after selling his FPGA IP company (Flex Logix), is now ‘self-employed’ on LinkedIn. I am interested in why Zero ASIC believes its FPGA IP products will be different. It’s a bit like Bullwinkle saying in ‘The Rocky and Bullwinkle Show’, ‘This time it’s for sure!’, or Charlie Brown kicking the football held by Lucy van Pelt again, only to have it fly away as usual, landing on his back.”Andreas Olofsson: “The eFPGA IP market is a niche market, so it’s not easy. IP is hard to do, and only a few vendors do it well. As a subset of this market, the eFPGA market has a high sales threshold, making it nearly impossible to grow.”That said, Zero ASIC is the first company to attempt an open architecture approach. We license our hard IP cores but allow anyone who wants to clone the architecture/bitstream (including our customers) to do so for free. This means customers will never be trapped in an architecture obsolescence situation (for example, if the company is sold or goes out of business).We will not compete with Xilinx/Altera in terms of original lookup tables (LUTs) or the richness of toolchain/IP features in the short term. Our success depends on several factors:Customers must appreciate our open philosophy. If they value PPA (power, performance, and area) over openness, then we still have room for improvement compared to competitors. eFPGA The market itself (how many customers can do something useful with 2K to 100K LUT cores?)Customers accepting our Python-based toolchain (no GUI, no TCL) and finding it “good enough.”I hope we can agree that RISC-V has made a significant change in the CPU space. The success of RISC-V stems from the market’s desire for openness. Whether FPGAs can achieve the same success remains to be seen.“Final note: Ultimately, our open eFPGA cores will also be offered in standardized chip forms (2mm x 2mm, 4.1mm x 4.1mm).”That’s all the details about Zero ASIC’s eFPGA products. Perhaps it is exactly what you need for your next ASIC or SoC design. Andreas Olofsson firmly believes it is.