1. Design Overview

This design implements a multi-channel UART/SPI communication system, capable of one-to-many communication. The system can operate in UART mode or SPI mode. The reason I chose this topic is mainly that my current laboratory needs to write a fast communication system based on UART. This topic can help solidify my previously learned knowledge and prepare me for future projects. Throughout this project, I mainly utilized knowledge about FPGA state machines, buses, and other aspects. This project can be applied in scenarios requiring high-speed asynchronous or synchronous serial communication, such as real-time control and monitoring.

When the system operates in UART mode, a single transmitter can send information to up to four receivers, with the valid information containing an address code. The receiver can determine whether the information is intended for itself based on the address code sent by the transmitter, achieving signal line multiplexing. UART communication is simple, requiring only one signal line; however, its drawback is that it only supports unidirectional communication, meaning the receiver cannot send data back to the transmitter. This limitation can be mitigated by using two UART systems.

When the system operates in SPI mode, communication can occur between one master and multiple slaves, and the system operates in full-duplex mode during communication. The master selects a slave by pulling down the chip select signal of one or more slaves.

2. System Composition and Function Description

The program implements communication for both UART and SPI, allowing mode switching via button presses. In UART mode, the transmitter sends a string of data to the receiver, which checks if it matches known data. If it matches, the LED lights up; if not, it remains off. In SPI mode, the master and slave send data simultaneously. If the received data matches known data, the LED lights up; if not, it remains off. Both UART and SPI have addressing capabilities. The addressing method for UART adds two address bits before the data bits to distinguish up to four receivers; the addressing method for SPI pulls down the SS signal of the selected slave to distinguish up to four receivers.

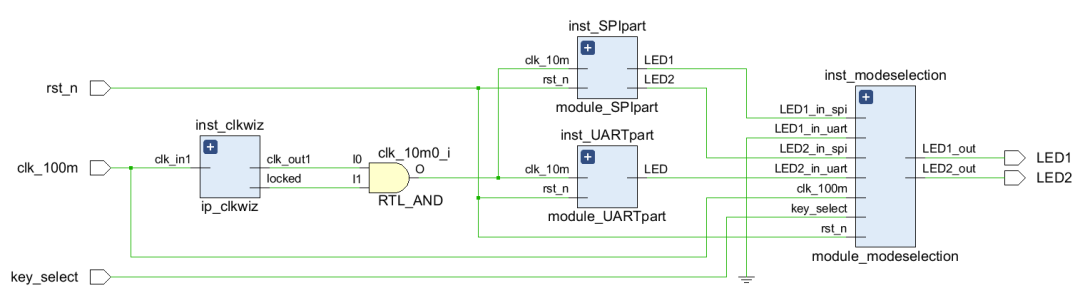

Currently, all functions have been implemented. The initial plan was to implement the communication system on two different FPGA boards, but one of the boards malfunctioned, so verification can only be conducted on one board. The transmitter and receiver, as well as the master and slave, are all written on one board, with internal communication lines directly connected using FPGA internal lines. The overall block diagram is as follows. Here, inst_clkwiz is the built-in frequency divider of the system, which reduces the external 100M signal to 10M, lowering the communication speed but making the communication system more stable; inst_SPIpart is the SPI communication module; inst_UART is the UART communication module; inst_modeselection is the communication mode selection module.

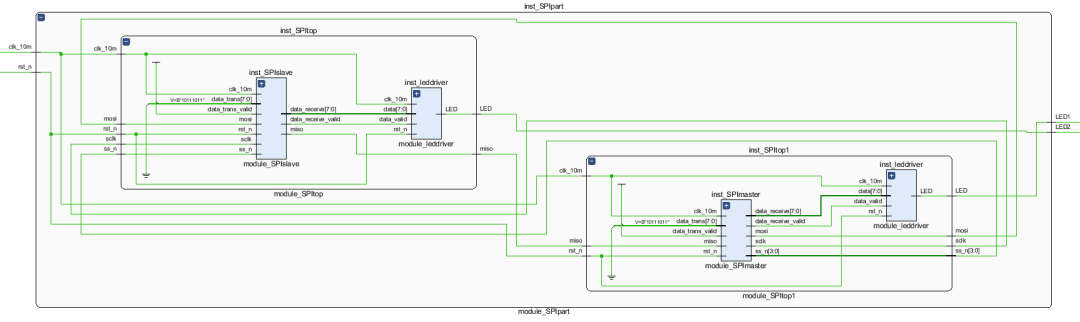

The internal structure of SPI is as follows. Here, inst_SPItop is the slave; inst_SPItop1 is the master. When the signal selection signal of the master is 0111, the slave in the system is selected. Inside the master and slave, inst_SPImaster is the SPI master port, inst_SPIslave is the SPI slave port, and inst_leddriver is the LED driver circuit responsible for determining whether the received signal matches the known signal. When the received signal matches the known signal, it drives the LED to light up.

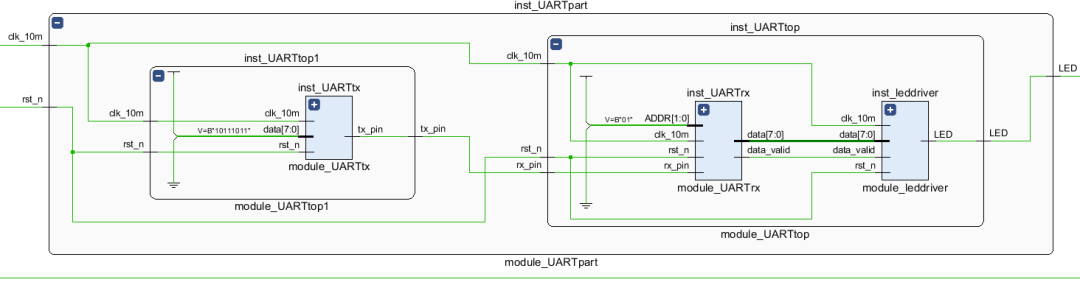

The block diagram of the UART part is as follows. Here, inst_UARTtop1 is the transmitter; inst_UARTtop is the receiver. The transmitter sends data to the receiver. When the receiver receives data that matches known data, it drives the LED to light up.

3. Completion Status and Performance Parameters

All functions can be implemented on one board, except for communication between two boards.

Testing Method:

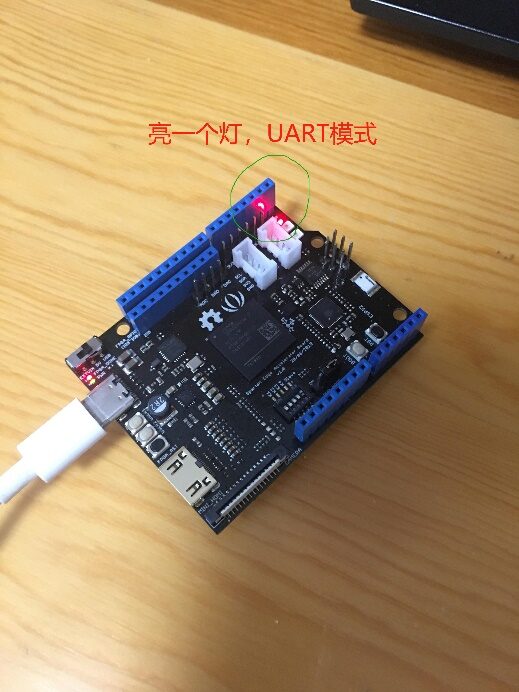

After powering on, press RST to reset the board. The default communication mode after reset is UART mode. The red LED lights up, indicating that in this mode, the receiver has received ten signals completely and completed the address determination. After passing the received signal to the LED driver module, it is judged to match known data 8’hbb. The LED2 signal is set, lighting up the red LED2, while the green LED1 remains off in UART mode. Based on these observations, UART mode operates correctly.

Pressing KEY1 lights up both the red and green LEDs, with the green LED dimmer than the red. The red LED indicates that the master successfully selected the slave, sent data to the slave, and the slave received the data sent by the master, matching known data. The green LED lights up, indicating the slave successfully sent data to the master, also matching known data. The green LED is dimmer than the red because the master only connected one slave, resulting in a match with known signals only 1/4 of the time, while during the remaining 3/4 of the time, it received 8’bzz, which does not match the known signal, keeping the LED off. Therefore, its brightness is lower.

Pressing KEY1 again switches the system back to UART mode, turning off the green LED and lighting up the red LED.

Due to recent changes in the WeChat public platform’s push rules, many readers have reported not seeing updated articles in a timely manner. According to the latest rules, we recommend frequently clicking “Recommended Reading, Share, Favorite,” etc., to become a regular user.

Recommended Reading:

-

Unrelated to Brake Failure? The Follow-Up on Tesla’s 11-Car Collision

-

Unexpectedly, the Kirin 9000s is produced in this Mysterious Park!

-

Breaking! Another Big Factory in Shenzhen Disbands: Layoffs Paid in N+1 Installments

Please click 【See】 to give the editor a thumbs up